面对日益复杂的AI推理任务与多样化的端侧需求,RISC‑V 凭借其灵活可扩展的架构特性,正成为 AI 时代的重要算力底座。然而,在RISC‑V高度碎片化的应用场景下, “如何在通用标准下做出差异化创新”成为关键命题,而答案往往藏在早期的处理器选型、 IP 评估与验证之中。

在近日举行的“2026 玄铁 RISC‑V 生态大会”上,阿里巴巴达摩院重磅发布全球最高性能 RISC‑V CPU IP——玄铁 C950,以及主打高能效的 C925 。自此,连同早前发布的C930,玄铁构建起新一代旗舰级 RISC‑V CPU 产品矩阵。其中,玄铁 C925 处理器在思尔芯第八代原型验证系统“芯神瞳 S8‑100”平台上完成首发展示。作为 C930 的能效优化版,C925 以更高性价比精准契合智能终端、工业控制等中低算力场景的规模化需求。

阿里达摩院首席科学家孟建熠在会上表示:“芯片企业的SoC设计往往需要高中低产品搭配,玄铁的这三张牌,正是为了给客户提供一站式的解决方案。”

面对玄铁高中低不同层级的处理器矩阵,思尔芯早已实现与玄铁全系列高性能处理器的深度适配。思尔芯副总裁陈英仁表示:“其实早在之前,我们就已经完成了与玄铁全系列高性能处理器的深度适配,R 系列与 C 系列均有成熟 Demo 验证。基于这一合作基础,思尔芯广泛的原型验证产品组合,可支撑从 IP 到系统的全场景验证,为玄铁及客户量身打造创新方案,加速先进 RISC‑V 芯片开发。”

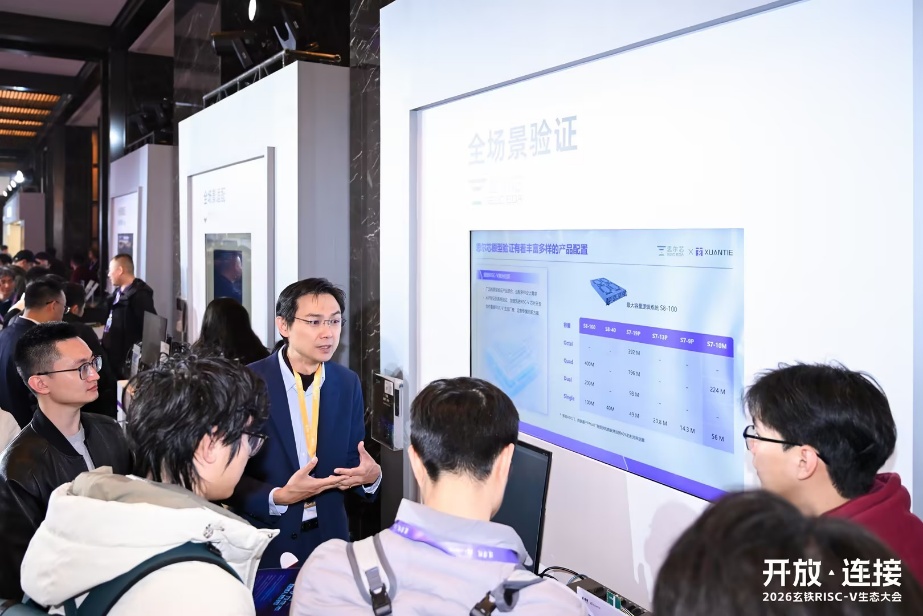

思尔芯副总裁陈英仁现场讲解

此次 C925 的首发演示,基于思尔芯第八代原型验证系统——芯神瞳 S8‑100(搭载 AMD VP1902 芯片)。该系统凭借创新的硬件架构与高性能 I/O 互联拓扑,显著提升了系统性能、数据吞吐量与验证效率;配合最新的 RTL 级分割编译、多系统调试、实时控制等软件工具,可快速部署复杂芯片或完整 SoC 的原型验证环境。同时,思尔芯还提供丰富的外设子卡、降速桥方案及快速定制服务,进一步加快系统搭建与验证节奏。

玄铁 C925基于思尔芯S8-100首发展示

这不仅是一次新品首发,更是玄铁与思尔芯共同打造的解决方案范式的延续。双方通过“左移”策略,将 IP 评估与架构选型前置到设计早期,从源头规避风险,打通从 IP 评估到应用场景的前端设计闭环。由此,芯片研发也从“确保芯片设计正确”,升级为“确保设计出正确的芯片”,从而有效加速研发进程,支撑复杂芯片创新高效落地。

事实上,双方的合作由来已久。玄铁 C907、R908 等高性能 IP 处理器此前均已在思尔芯原型验证系统上完成验证和展示,技术协同与生态互信持续加深。

值得关注的是,玄铁今年的一个重要变化,是从底层软件走向更明确的下游应用场景,主动寻找细分赛道、头部客户与垂直行业标杆。因为只有从真实应用需求中生长出来的创新,才能在场景中建立真正的竞争力,而非停留在概念层面的“生态话术”。

“‘标准化’曾是工业时代的皇冠,但在 RISC-V高度碎片化的今天,它正逐渐成为一种枷锁。如何在通用标准之下实现快速创新?”思尔芯副总裁陈英仁指出:“没有任何一家公司能独自完成全部工作。客户希望获得面向新技术与新应用的完整解决方案,以支持自身产品的快速迭代——这需要 EDA 工具在早期就介入验证与评估,也正是 EDA 的核心价值所在。”

基于此,思尔芯积极构建开放生态,与玄铁等行业头部伙伴深度协同,将 IP、架构、评估与应用场景提前纳入前端设计闭环,帮助复杂芯片创新从理念走向现实。此前,双方共建的玄铁IP评测中心,已实现从 IP 到系统的全场景验证,为 RISC‑V 生态注入更多确定性。

当算力需求日益碎片化,EDA 与 IP 的深度协同将成为破局关键。思尔芯正通过与玄铁的紧密合作,持续推动 RISC‑V 从“可用”走向“好用”,为 AI 时代的新兴应用筑牢底层算力基石。在算力重构的时代节点上,思尔芯正与玄铁一道,让每一次底层创新都拥有落地的路径。