中科院微电子所集成电路先导工艺研发中心殷华湘/吴振华研究团队日前在国际学术期刊发表研究成果,利用DTCO(设计工艺协同优化)工程思想全面探索了互补场效应晶体管(CFET)的器件架构优势。

根据该所介绍,CFET结构是对新一代先进制程节点环栅(GAA)晶体管的进一步改进,将不同导电沟道类型的GAA器件在垂直方向进行高密度三维单片集成,从而突破了传统N/P-FET共平面布局间距的尺寸限制,在3纳米以下技术代高密度、高性能集成电路制造技术中是器件创新架构的有力候选者。

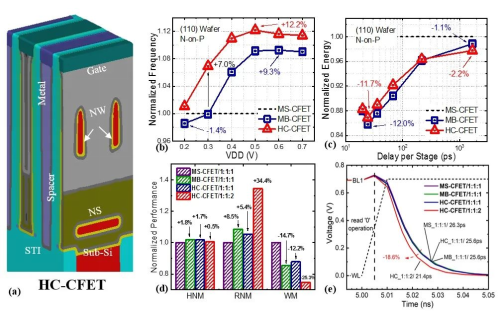

该所研究团队依托其提出的新型混合沟道CFET(Hybrid Channel Complementary FET,HC-CFET)结构设计和集成方案,利用SiNx与SiO2的高刻蚀选择比,通过分步沟道形貌刻蚀,实现对N-FET和P-FET首选高电子与空穴迁移率导电沟道的共同优化,即使得N-FET具有(100)沟道表面晶向,P-FET具有(110)沟道表面晶向,从而在同等投影平面下获得最佳的器件与电路性能。

目前,该结构设计与集成方案的可行性已通过Virtual-FAB模拟仿真验证,展现出更高的工作频率以及更优的噪声容限窗口,以及在高度微缩的高性能CMOS集成电路应用上的巨大潜力。(校对/Aileen)