本文从半导体制造流程引入,介绍了CoWoS(Chip on Wafer on Substrate)技术的概念、特点和优势,并描述了CoWoS技术的主要流程。

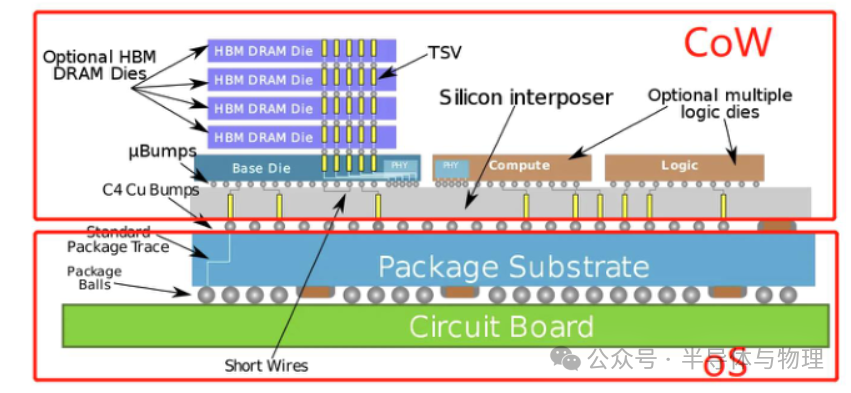

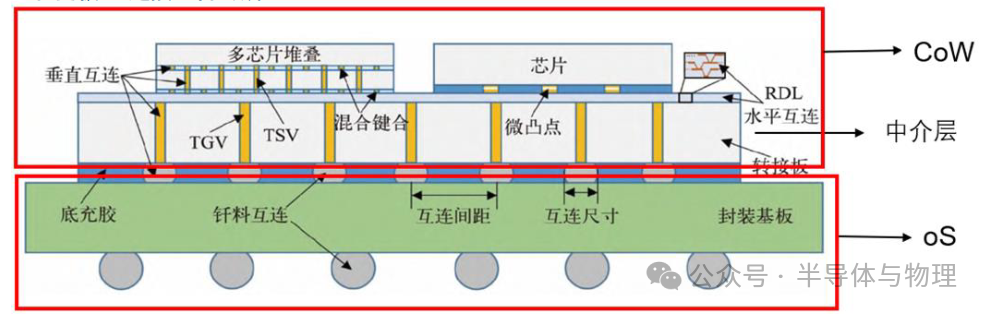

CoWoS(Chip on Wafer on Substrate),即芯片在晶圆上再连接到基板的技术,是一种先进的2.5D封装解决方案。它能够将多个不同功能的芯片,如处理器、内存和其他专用集成电路,堆叠并集成在一个基板上,形成一个紧凑且高效的单元。

随着摩尔定律逐渐接近物理极限,传统的前道制程工艺发展受限。为了应对这一挑战,越来越多的企业开始转向后道先进封装工艺,寻求通过创新的封装技术来持续提升产品的性能。在这个背景下,2.5D封装和3D封装等先进封装技术应运而生,成为延续芯片性能提升的重要途径之一。

半导体制造的主要阶段

半导体制造过程可以分为三个主要阶段:前道、中道和后道。每个阶段都对最终产品的性能和质量起着至关重要的作用。

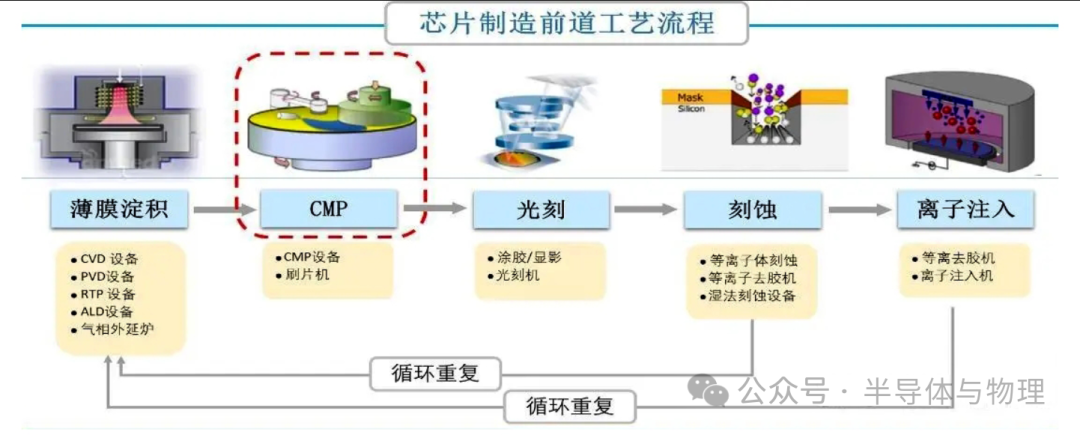

前道(Front-End Manufacturing):这一阶段主要涉及晶圆制造,在空白的硅片上完成电路加工的过程。这包括光刻、刻蚀、薄膜生长、离子注入、清洗以及CMP等一系列复杂的工艺步骤。

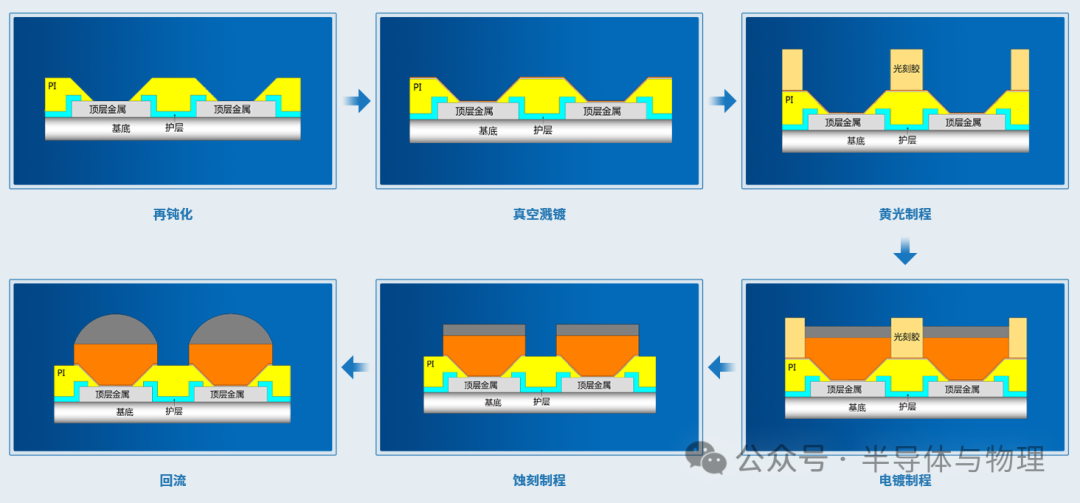

中道(Middle-End Manufacturing):中道是介于晶圆制造和封装测试之间的一个关键环节,有时也被称作“Bumping”。它通常指的是在晶圆上形成的凸点(Bumps),这些凸点用于后续封装过程中实现芯片与外部电路的连接。随着高密度芯片需求的增长,尤其是倒装芯片(Flip-Chip)技术的应用,中道制造变得越来越重要。

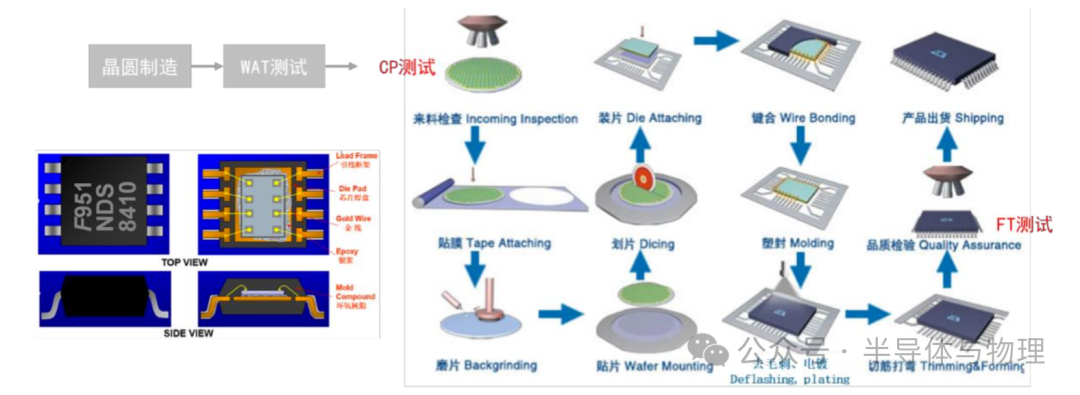

后道(Back-End Manufacturing):后道工艺涵盖了从减薄到终测的所有封装和测试活动。具体操作包括将圆形硅片切割成单独的芯片颗粒,进行外壳封装,执行引线键合或倒装焊接,实施模塑保护,以及进行全面的测试以确保产品质量。

CoWoS技术的特点与优势

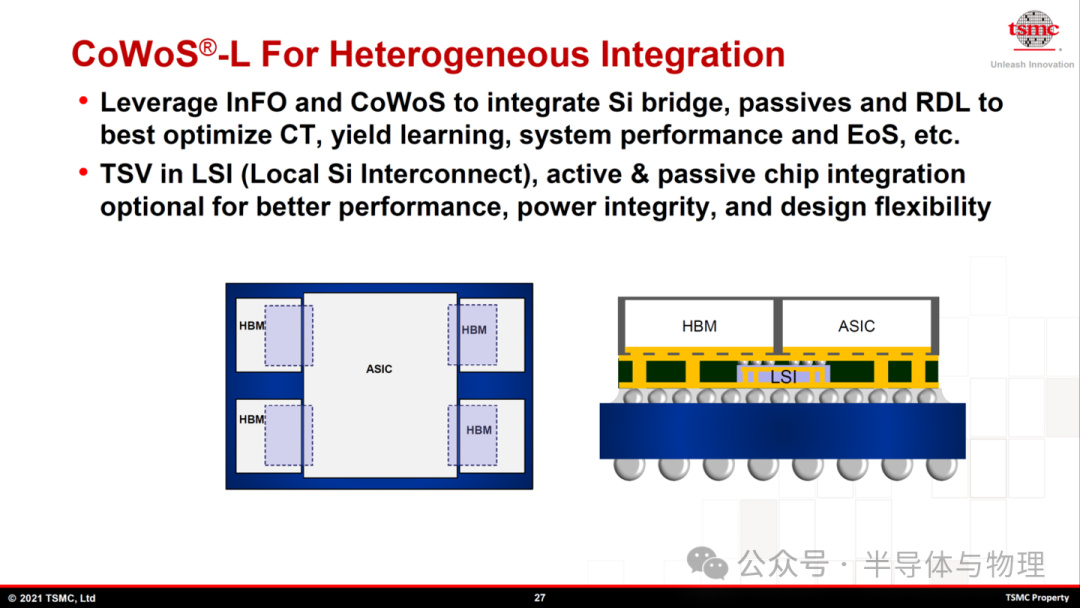

CoWoS严格来说属于2.5D先进封装技术,其核心在于将不同的芯片堆叠在同一片硅中介层上,实现多颗芯片之间的高效互联。相比传统的封装方式,CoWoS具有以下显著特点:

高度集成:CoWoS允许在一个封装内集成多个异构芯片,从而实现更高的系统级集成度。例如,它可以同时集成逻辑处理单元和高带宽内存(HBM)。

高速传输:通过硅中介层上的微小金属线,CoWoS实现了不同芯片间的紧密连接,极大地提高了数据传输速度和带宽。

灵活性强:CoWoS可以根据具体应用需求灵活选择不同的芯片组合,支持多种类型芯片的混合搭配。

散热优异:相较于传统封装方式,CoWoS能更好地分散热量,有助于维持系统的稳定运行。

CoWoS的具体流程

CoWoS技术的具体流程如下:

Chip on Wafer (CoW):首先,通过特定的封装制程将芯片连接至硅晶圆。这一过程确保了芯片能够在硅中介层上正确排列,并为后续的互联做好准备。

Wafer on Substrate (WoS):接下来,将已经过CoW处理的芯片与基板连接起来。这个步骤涉及到将整个硅中介层及其上的芯片作为一个整体转移到基板上,完成最后的封装整合。

互联实现:在硅中介层中,台积电使用微凸块(μBmps)、硅通孔(TSV)等技术代替传统引线键合用于裸片间连接,大大提高了互联密度以及数据传输带宽。