当前,边缘智能计算设备在部署神经网络时,通常需要通过训练微调来提高网络的准确性。然而,依赖远程云端进行训练的方法存在高延迟、高能耗以及隐私泄露风险等缺点,因此,开发支持本地训练的存算一体技术至关重要。传统的存算一体宏仅支持网络推理,无法进行网络训练所需的转置运算。现有方案在训练过程中的前向和反向传播阶段,无法有效复用乘累加电路,导致功耗和面积的浪费,并且仅支持定点数制的模拟存算方案,在精度上也存在较大不足。如何有效实现支持转置操作的高能效、高精度的存算一体宏,是当前存算一体领域亟待解决的问题。

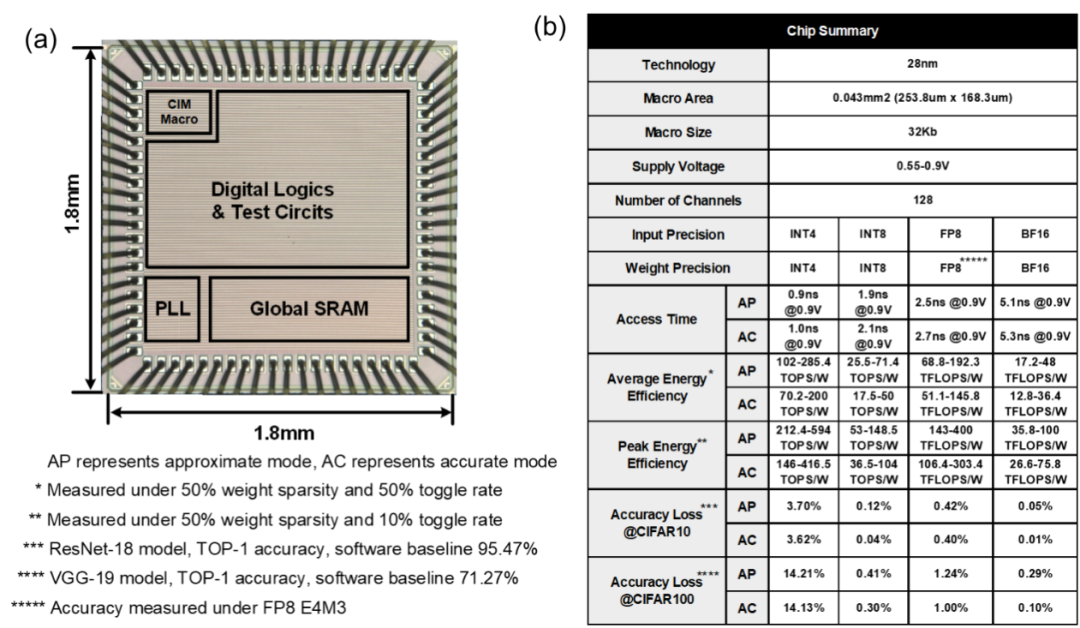

针对这些挑战,集成电路制造技术全国重点实验室的张锋研究员团队设计了一款可转置的近似精确双模浮点存算一体宏芯片。通过创新的循环权重映射SRAM方案,该芯片在前向与反向传播时能够复用乘加单元,在实现转置功能的同时,大幅提升了能效与计算密度。通过引入有符号定点尾数编码方式和向量粒度预对齐方案,芯片实现了多种浮点和定点数制的兼容支持,相较于传统的粗粒度浮点预对齐方案,精度损失更小。芯片的近似精确双模乘加电路设计,使其在推理环节精度要求较低时可开启近似模式,提升12%的速度并降低45%的能耗;在训练环节精度要求较高时,则开启精确模式以确保无精度损失。该存算一体宏芯片在28nm CMOS工艺下流片,支持BF16、FP8浮点精度运算及INT8、INT4定点精度运算。BF16浮点矩阵-矩阵-向量计算的平均能效达到48TFLOP/W,峰值能效达到100TFLOPS/W;FP8浮点矩阵-矩阵-向量计算的平均能效达到192.3TFLOP/W,峰值能效达到400TFLOPS/W。这一研究为边缘端训练的存算一体架构芯片提供了新的思路。

上述研究以“A 28nm 192.3TFLOPS/W Accurate/Approximate Dual-mode Transpose Digital 6T-SRAM Compute-in-Memory Macro for Floating-Point Edge Training and Inference”为题入选ISSCC 2025。微电子所博士生袁易扬为第一作者,张锋研究员与北京理工大学李潇然助理教授为通讯作者。该研究成果得到了科技部重点研发计划、国家自然科学基金、中国科学院战略先导专项等项目的支持。

图1. 28nm 基于外积的数模混合浮点存算一体宏芯片:(a)芯片显微镜照片,(b)芯片特性总结表。