异质集成晶圆级键合技术是指在半导体制造过程中,通过特定的W2W、D2W、HB & TSV等工艺,将不同材质或特性的晶圆材料直接键合在一起的技术。在当今信息爆炸的时代,数据处理能力和传输速度的需求日益增长,传统的单一材料芯片已经难以满足需求。异质集成晶圆级键合技术可将具有不同物理特性和功能的材料进行高精度、高强度连接,从而允许在单个芯片上集成多种功能,如计算、传感、通信等,极大地提高芯片功能密度和性能,实现芯片性能的飞跃。由此,不仅促进了高性能计算、高速通信、智能传感等领域的快速发展,也为新型电子产品的研发提供了新的可能。主要技术方向包括直接键合、金属间键合、共晶键合、聚合物键合等。该技术正朝着更高精度(亚微米)、更低成本、更大规模(多颗粒、系统级)生产的方向发展。此外,随着新材料(如二维材料、超宽禁带半导体等)的不断发现和应用,异质集成技术的应用范围将进一步扩大,有望在未来的信息技术领域发挥更加重要的作用。

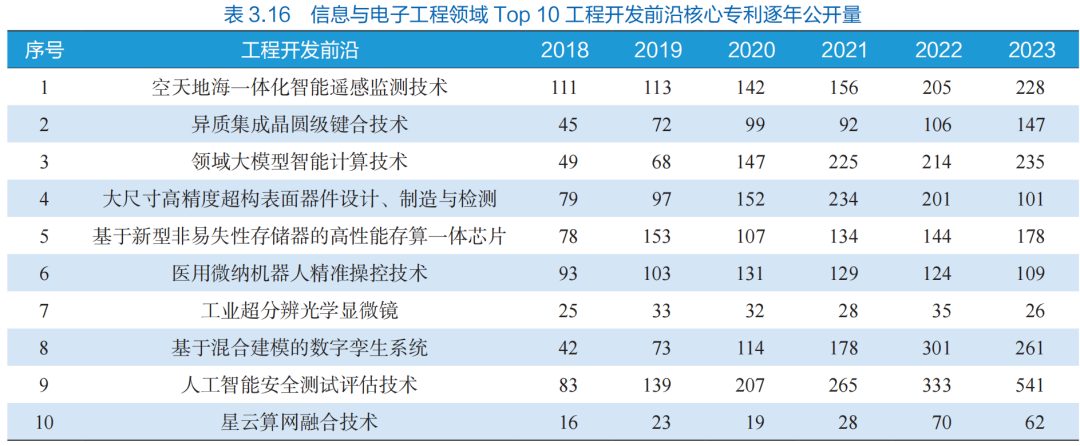

该前沿主题2018—2023年间发表的核心论文(注:针对该主题在Web of Science检索得到的被引频次位于前10%的高影响力论文——截至2023年12月)数量及其逐年发表情况见表3.15和表3.16。

20世纪末以来,随着纳米技术和微加工技术的进步,异质集成晶圆级键合技术得到了迅速发展。2016年,日本索尼公司公开报道了基于Cu/SiO2混合键合技术的背面照明互补金属氧化物半导体器件(CMOS)图像传感器IMX260,该传感器被应用于三星手机Galaxy S7。针对异质晶体管 / 芯片高密度集成难题,2018年,美国Teledyne等公开报道了基于晶圆级Cu/SiO2混合键合技术实现的250 nm InP HBT与Si CMOS的异质集成,并演示了高性能毫米波集成电路。台湾积体电路制造股份有限公司推出了三维芯片堆叠技术的集成片上系统(SOIC)方案,该方案平台应用于N7-on-N7、N5-on-N5、Logic-on-DTC等,以提升计算带宽与电源优化;同时期,武汉新芯集成电路股份有限公司推出了基于高密度混合键合W2W与C2W的晶圆级异构集成系列平台,为传感器、存储与算力提升提供了更多选项。

近年来,随着各主要工艺厂商的异质集成方案逐渐成熟,英特尔、AMD、苹果、NVIDIA等公司相继推出了异质集成产品方案,并获得了市场的广泛认可。从最初的实验探索到现在的商业化应用,异质集成技术经历了从简单结构到复杂系统、从低效手工操作到高效自动化生产的转变。未来,随着5G、物联网、人工智能等新兴领域的快速发展,对高性能、多功能集成芯片的需求将更加迫切,这将推动异质集成技术向更精细、更高效的方向发展。

目前,全球范围内有许多研究机构和企业在进行异质集成技术的研究与开发工作。美国、日本、欧洲等地的一些顶尖大学和科研机构,如麻省理工学院、东京大学、德国弗劳恩霍夫研究所等,在该领域处于领先地位。与此同时,中国也加大了对该技术的研发投入,一些知名企业和高校如华为、清华大学等也在积极布局相关研究。

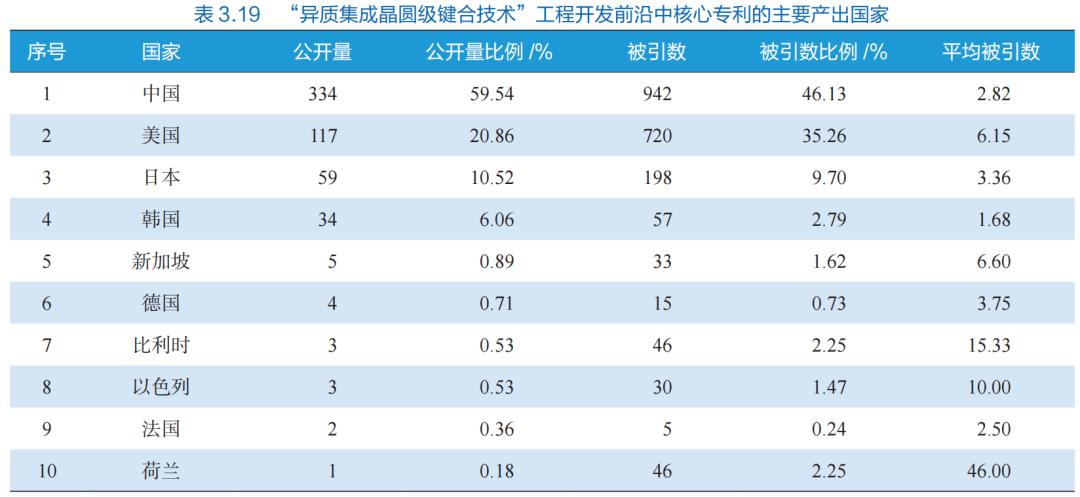

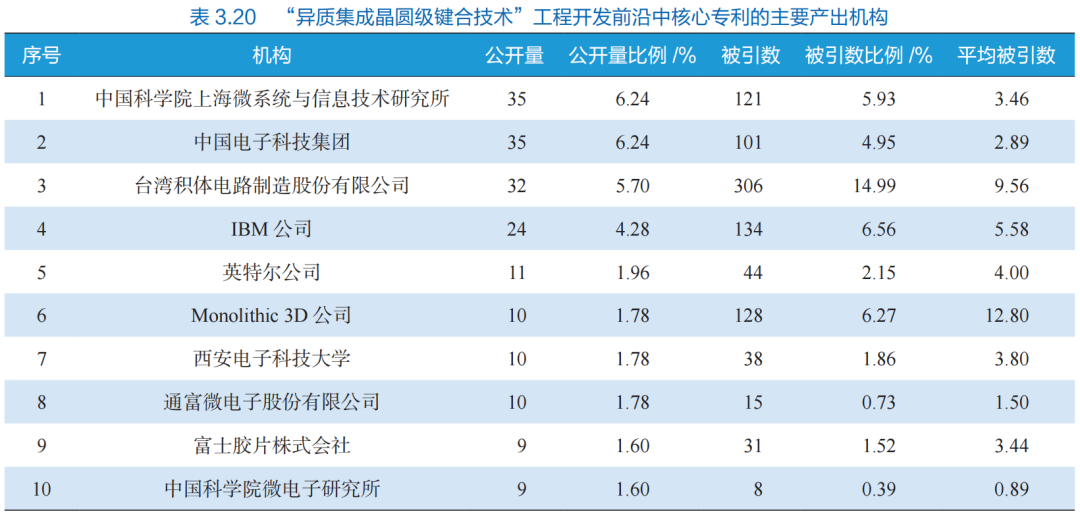

“异质集成晶圆级键合技术”工程开发前沿中核心专利的主要产出国家见表3.19。中国专利公开量约占总数的60%,但平均被引数仅排名第八。美国以20.86%的占比处于第二位。日本和韩国也有一席之地。荷兰、比利时和以色列虽总量较低,但平均被引数表现出色,展现了较高的专利质量与技术价值。该前沿核心专利的主要产出机构见表3.20,中国科学院上海微系统与信息技术研究所、中国电子科技集团和台湾积体电路制造股份有限公司位列公开量三甲;从平均被引数看,Monolithic 3D公司和台湾积体电路制造股份有限公司显著领先,IBM公司位列第三。

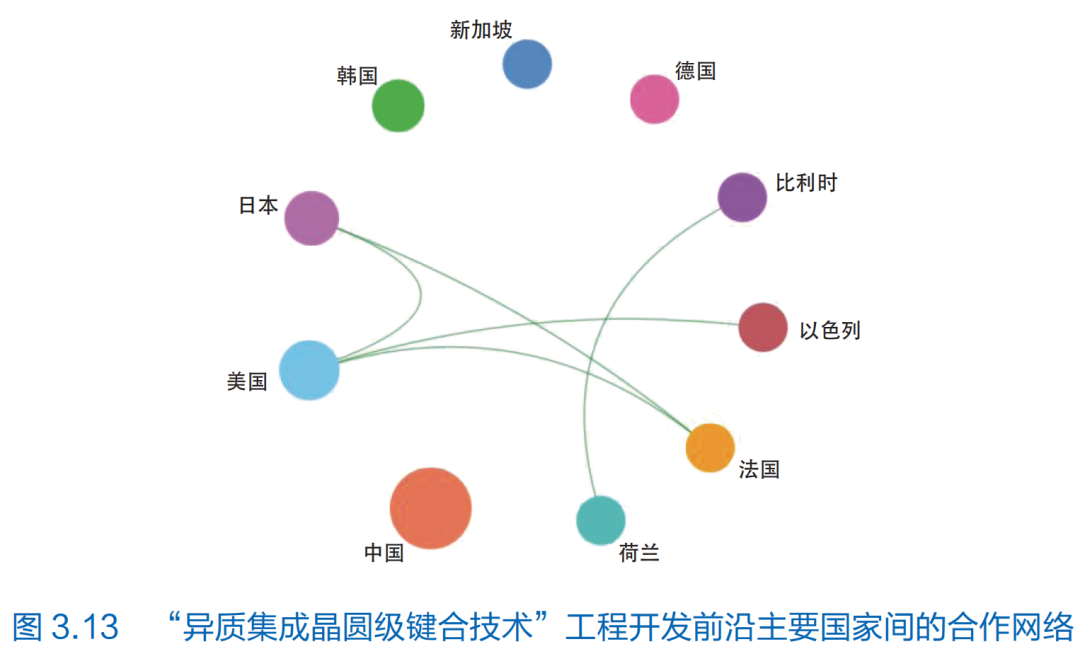

异质集成技术涉及材料科学、微纳加工等多个学科领域,是芯片制造的一项关键技术,对信息技术的发展具有重要意义。图3.13显示,美国、日本与法国三者互相合作密切,荷兰与比利时之间也有交流合作,其他国家对外交流合作有待加强。

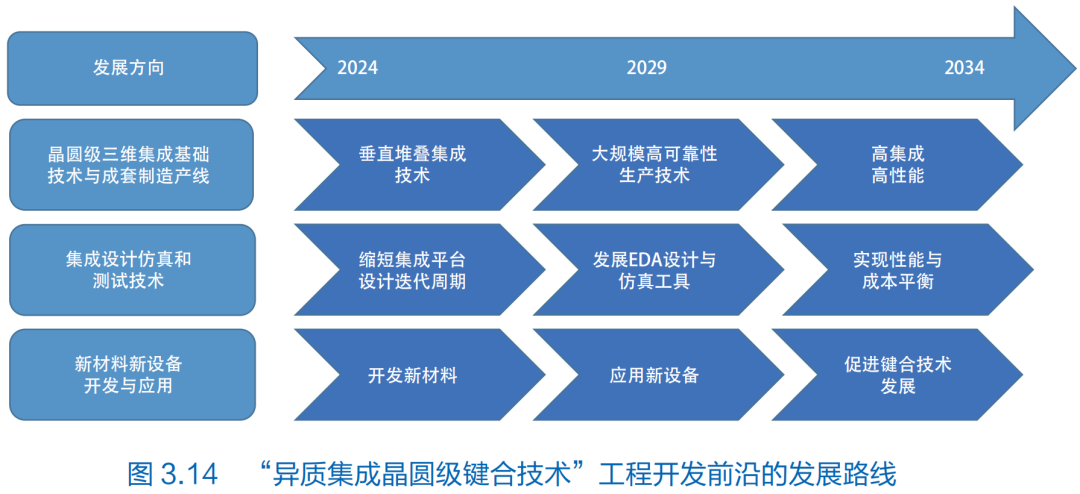

“异质集成晶圆级键合技术”未来5~10年的重点发展方向(图3.14)如下:

(1)晶圆级三维集成基础技术和成套制造产线

1)垂直堆叠集成技术:包括高密度微尺寸硅通孔技术、背面供电技术、纳米级键合间距混合键合技术(特别是芯片到晶圆的键合技术),通过在垂直方向上堆叠不同功能和更多层的芯片,实现更高的集成度和性能。

2)大规模高可靠性生产技术:提高键合精度和一致性,确保大规模生产中的高良品率;开发高效的自动化生产线,降低生产成本,提高生产效率。

(2)集成设计仿真和测试技术

1)异质集成系统体系的热、应力、电磁、信号、压降、静电放电(ESD)防护等方向的联合设计与仿真优化技术,有助于提升集成平台的设计迭代周期和可靠性。

2)发展电子设计自动化(EDA)设计与仿真工具,如实现多芯片、跨制程、不同物理场的设计仿真文件互通,为联合设计仿真优化(DTCO)提供支持。

3)晶圆级集成系统需在单芯片测试、集成后测试、封装终端测试前做好测试设计,并诊断相应芯片和三维互连问题。通过快速测试和筛选,评价系统性能和成本平衡。

(3)新材料新设备的开发与应用

1)工艺新材料:针对异质集成系统中不同介质材料热膨胀系数差异大导致的应力问题,开发具有高键合强度的界面材料;同时,为应对日益提高的功耗密度带来的散热挑战,开发高导热系数的新型填充材料和界面材料。

2)工艺新设备:①关键工艺设备——用于实现高精度D2W键合集成的新型键合设备;用于实现Die间高深宽比填充和极高选择比的平坦化设备、晶边处理设备、应力调整设备等②检测设备——异质集成翘曲变形、应力检测分析设备;高深宽比TSV的无损三维检测技术;快速的表面形貌检测、建模技术,以预测/优化键合工艺参数。

预计在未来5~10年内,随着上述重点发展方向的突破,异质集成晶圆级键合技术将在高性能计算、量子信息处理、生物医疗设备等领域展现巨大的应用潜力。特别是在量子计算机、神经形态计算等前沿科技领域,有望成为推动领域快速发展的核心技术之一。同时,随着技术成熟度的提高和成本的降低,其在消费电子产品中的应用也将越来越广泛,为人们的生活带来更多便利。

总之,异质集成晶圆级键合技术在未来5~10年里将保持快速发展态势,通过新材料应用、三维集成技术突破、大规模生产技术改进以及跨学科融合,为信息技术领域带来革命性变化。