2025年5月24日至27日, 新思科技受邀参与深圳大学电子与信息工程学院、IEEE电路与系统深圳分会联合举办的“数字集成电路中后端设计流程与EDA工具实战培训”。本次培训面向40余名集成电路工程专业研究生,由新思科技资深工程师团队全程授课,通过系统化课程设计为学子打通从理论到产业实践的进阶通道。

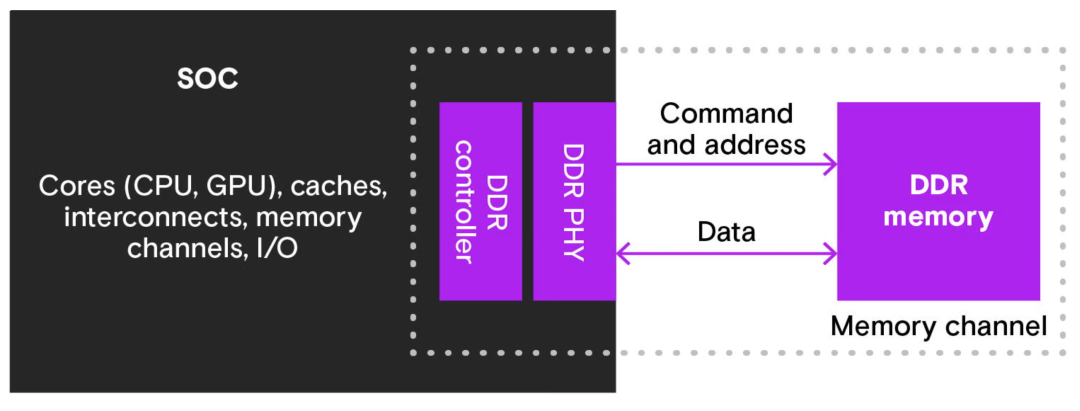

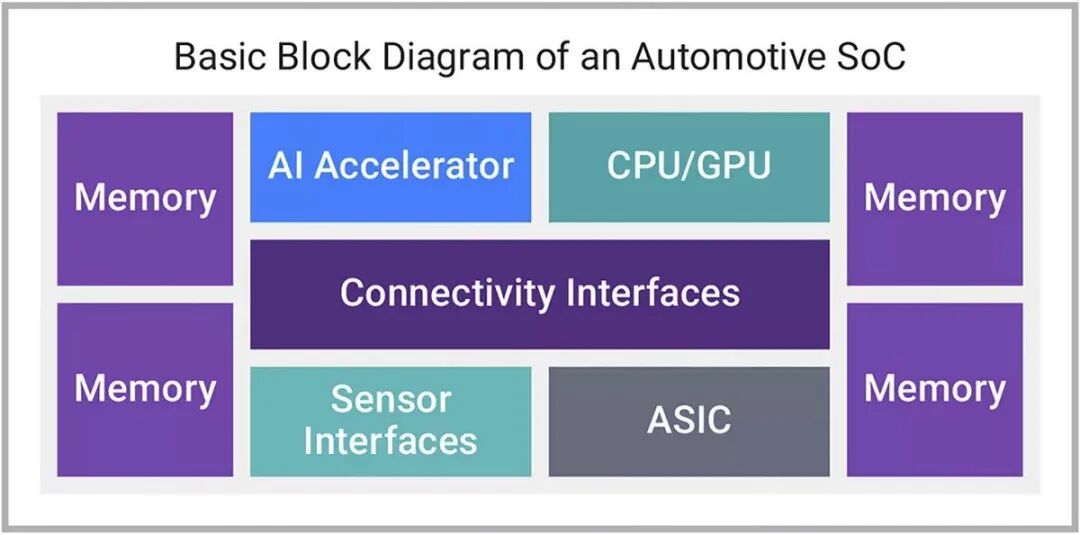

在人工智能(AI)时代,数字芯片和逻辑芯片的设计与实现显得尤为重要。与单片机嵌入式系统和FPGA的开发流程不同,数字集成电路的中后端设计(从逻辑网表到版图生成、物理验证及签核)对专业性和技术复杂度的要求极高。这一阶段涉及逻辑综合后的物理实现、时钟树综合、布线、时序分析、功耗分析、物理验证等关键步骤,需要开发者熟练运用一系列先进的EDA工具软件,以确保芯片的可靠性、功能性和性能达到设计要求。

此次实战培训旨在为未来开发者提供一个系统学习和深度实践数字集成电路中后端设计流程及其核心EDA工具的机会,帮助他们在未来的学术和职业生涯中打下坚实基础,更好地应对技术挑战。

培训采用“理论+实践”的强化模式。新思科技的资深工程师们为学生们带来了关于数字集成电路中后端设计流程的全面讲解。内容系统覆盖了从逻辑网表输入、物理实现(布局规划、布局、时钟树综合、布线)、时序/功耗分析(Signoff)到物理验证(DRC/LVS)等核心环节,并着重介绍了新思科技Fusion Compiler(物理实现)和PrimeTime(签核级静态时序分析)两大核心工具在流程中的关键作用和应用技巧。

工程师们在理论讲解中系统梳理了数字集成电路设计全流程,并聚焦于中后端部分,深入阐释了硬件描述语言(HDL)综合后得到的逻辑网表如何作为中后端设计的起点,并详细拆解了使用Fusion Compiler进行物理实现(包括布局规划、标准单元布局、时钟树综合、全局与详细布线)以及使用PrimeTime进行签核级时序分析、功耗分析的关键步骤、挑战与最佳实践。

工程师们特别强调了集成电路设计专业工具如Fusion Compiler和PrimeTime在整个中后端设计流程中的核心枢纽作用。这些工具贯穿了从网表到GDSII的物理实现、优化与验证全过程,并结合具体案例,分享了在真实项目中使用Fusion Compiler实现高质量布局布线、优化功耗和面积,以及运用PrimeTime进行精准时序签核、功耗分析和ECO(工程变更命令)流程的经验与技巧,强调了精通这些工具对大幅缩短设计周期、提升设计一次成功率(First-Pass Success)的重要性。

此外,工程师们在理论课和实操指导中还重点讲解了数字集成电路中后端设计中涉及的可靠性(如电迁移、IR Drop分析)、功能性(通过形式验证等价性检查确保网表一致性)和性能(通过PrimeTime进行严格的建立/保持时间、时钟偏斜等时序签核)验证环节。他们指出,这些环节是确保芯片设计成功流片的关键,尤其是在AI和高性能计算领域,芯片的可靠性、功耗和性能指标直接影响到最终产品的市场竞争力。

上机实操环节,在工程师的现场指导下,学生们分组动手实践,利用Fusion Compiler和PrimeTime工具链,在真实的工业级设计环境和示例项目上,演练了所学的物理实现流程、时序分析、功耗优化等关键技术。工程师们深入探讨了学生们在实操中遇到的数字集成电路中后端设计常见挑战,并提供了即时的解决方案和优化建议。特别是在AI和高性能计算领域,芯片设计的复杂性和性能要求越来越高,工程师们结合实例分享了应对这些挑战的策略。

培训结业仪式上,为所有顺利完成培训的学生颁发了结业证书,并评选出表现优异的学员授予“优秀学员”证书。最后,全体参与培训的师生与新思科技工程师团队合影留念,为此次充实的培训画上圆满句号。

培训过程中,同学们展现出极高的学习热情。就Fusion Compiler和PrimeTime的具体操作、中后端设计中的常见难点(如时序收敛、功耗优化、物理规则违例修复)以及未来EDA工具和设计方法学的发展趋势向工程师们积极提问。工程师们耐心细致地解答了每一个问题,并鼓励同学们在后续的课程设计和项目中多动手实践,深入钻研工具,积累宝贵的项目经验。许多同学表示,通过此次系统性的实战培训,他们对数字集成电路中后端设计的全貌有了清晰的认识,特别是对Fusion Compiler和PrimeTime等工业级核心EDA工具的实际应用能力得到了显著提升。

本次“数字集成电路中后端设计流程与EDA工具”实战培训的成功举办,是新思科技强化产学研生态联动,与高校深化合作的一次典范实践,为未来开发者构建直面产业需求的实战能力矩阵,为培养未来集成电路领军人才奠定坚实基础。新思科技一直致力于加速万物智能时代的到来,为全球创新提供值得信赖的、从芯片到系统的全面设计解决方案,涵盖电子设计自动化(EDA)、半导体IP 以及系统和芯片验证。新思科技将继续探索产教融合新路径,为创新提供源动力,让明天更有新思。