随着 5.5G/6G 无线通信技术不断迭代和下一代 Serdes 接口朝更高传输速率发展,毫米波本振时钟的抖动性能面临前所未有的严苛要求。亚采样锁相环凭借其天然的高鉴相增益优势,已成为低抖动时钟芯片的主流技术路线。然而,传统方案仍存在诸多技术瓶颈:电荷共享效应严重损害环路相位裕度,需大幅提高主从采样电容比值,导致隔离缓冲器功耗激增;为抑制二进制频移键控效应对参考杂散的影响,传统架构必须引入额外的 dummy 采样路径,进一步增加功耗负担;毫米波频段下,电容与变容管的品质因数偏低,使振荡器相位噪声恶化,直接影响锁相环的整体抖动表现。

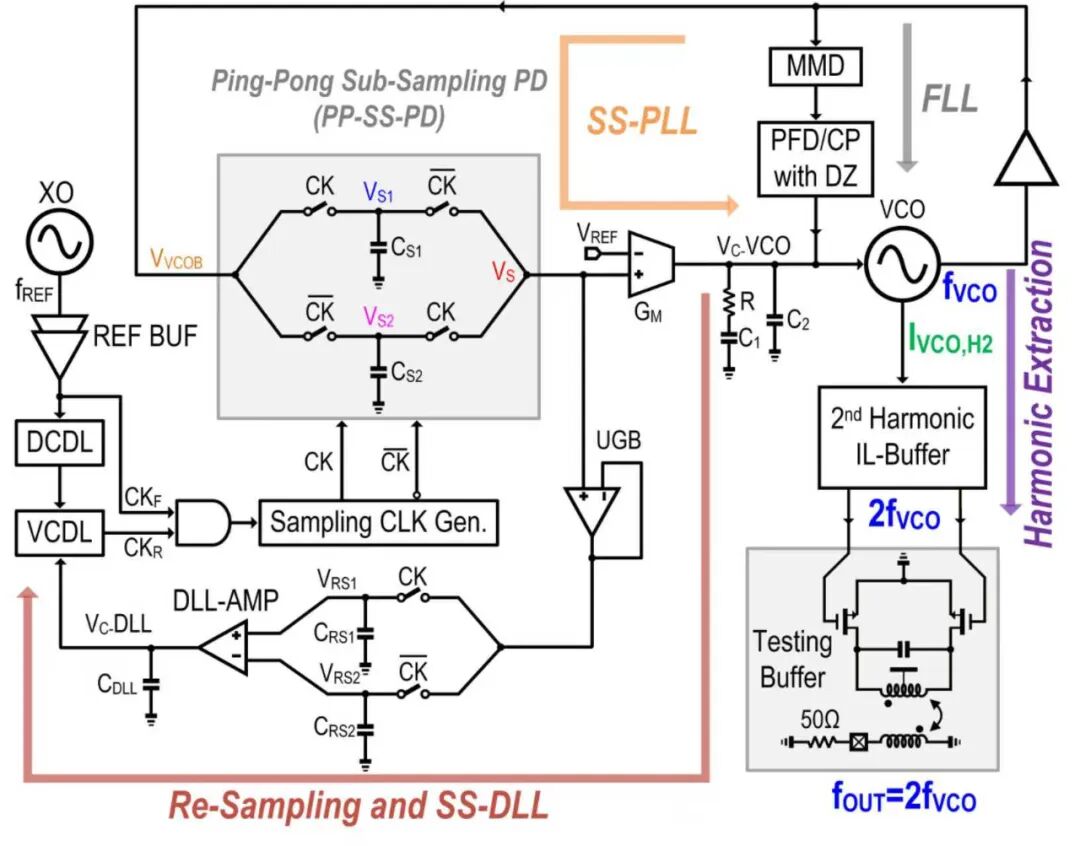

针对这些关键技术难题,中国科学院微电子研究所抗辐照器件技术重点实验室杨尊松、黄云波团队联合清华大学,开创性地提出了双边沿乒乓亚采样锁相环架构。该创新设计巧妙利用参考时钟的上升沿与下降沿,实现参考频率的等效倍频,成功解决了传统亚采样锁相环在环路带宽、带内相位噪声与参考杂散之间的设计矛盾。研究团队还开发了一种高效率的注入锁定缓冲器方案,该方案在高效提取振荡器二次谐波的同时实现谐波整形,显著降低了锁相环的带外相位噪声。

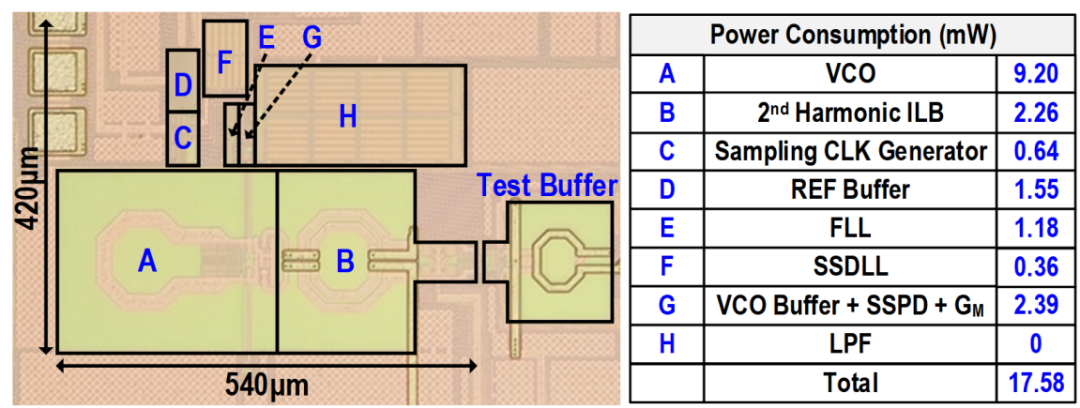

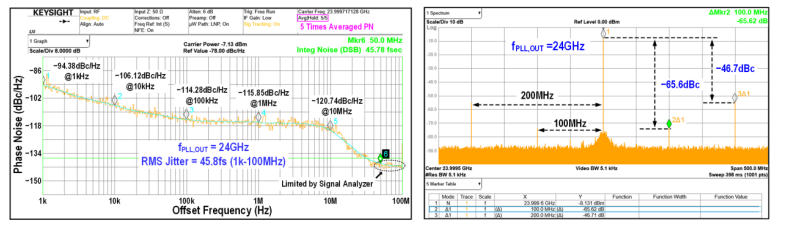

基于这些前沿技术,团队采用 65nm CMOS 工艺成功研制了一款 K 波段锁相环时钟芯片,输出频率覆盖 22.4–25.6 GHz,整体功耗仅为 18 mW,RMS 积分抖动优于 50 fs,抖动-功耗优值(FoM)达到 −254 dB 以下,处于国际领先水平。

该研究获得了国家自然科学基金的资助,相关成果以"A 22.4–25.6 GHz Ping-Pong Sub-Sampling PLL Featuring Unified Supply Voltage Level and Balanced 2nd Harmonic Extraction"为题,发表在集成电路设计领域顶级期刊《IEEE Journal of Solid-State Circuits》上。微电子所副研究员黄云波为论文第一作者。

图1 乒乓亚采样锁相环电路结构

图2 锁相环芯片照片及各模块功耗

图3 锁相环芯片相位噪声及参考杂散测试性能