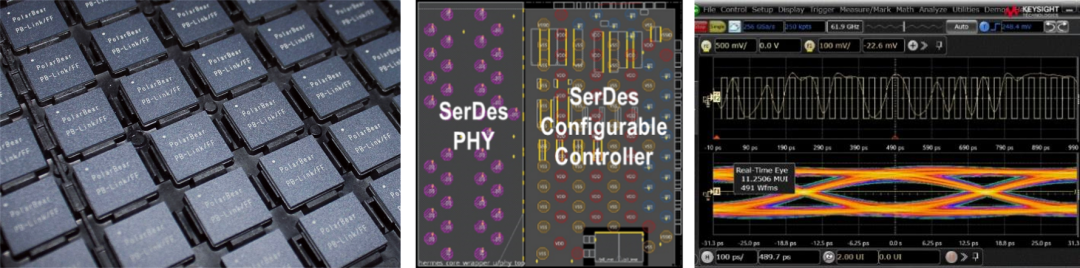

北极雄芯9月6日宣布,自主研发的首个基于国内《芯粒互联接口标准》的Chiplet互联接口PBLink回片测试成功。PBLink接口具备低成本、低延时、高带宽、高可靠、符合国产接口标准、兼容封装内外互连、注重国产自主可控等特点。

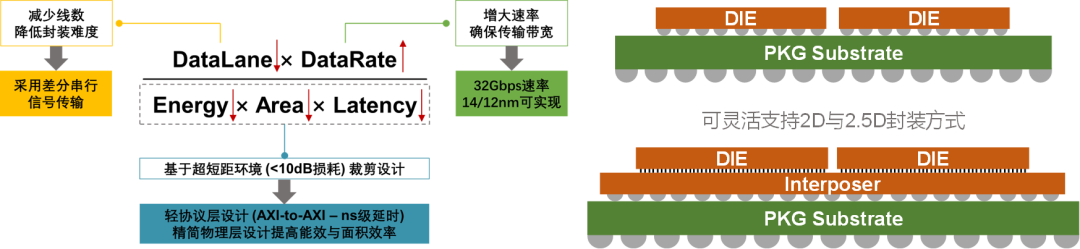

根据官方介绍,PBLink接口采用12nm工艺制造,每个D2D单元为8通道设计,合计提供高达256Gb/s的传输带宽,可采用更少的封装互连线以降低对封装的要求,最少仅需要3层基板进行2D互连;基于专门优化的精简协议层和物理层,可实现ns级别的端到端延迟,各项指标符合《芯粒互联接口标准》要求及设计预期;此外,PB Link可灵活支持封装内Chiplet–Chiplet互联以及10-15cm的封装外板级Chip–Chip互联,灵活适配各类下游应用场景需求。

北极雄芯率先推出的是基于传统封装(153μm Standard Package)的芯粒解决方案,并预计在2024~2025年推出针对超高性能场景的高密度互连版本(55μm InFO Package)。

北极雄芯于2023年初发布了国内首款基于Chiplet异构集成的人工智能计算芯片“启明930”,并持续投入各类通用型HUB Chiplet,功能型Chiplet以及高速芯粒互联接口的研发。本次回片测试成功的PBLink将用于公司下一代核心HUB Chiplet以及部分功能型Chiplet上,预计于2024年内实现整体量产。

据悉,Chiplet架构是将多颗不同功能、不同制程的芯粒封装在一起,能够有效解决大面积芯片面临的良率低、量产成本高等问题,亦可面向不同场景需求提供灵活的组合。目前,苹果、英伟达、AMD、英特尔、华为等皆在最新产品上应用Chiplet架构。

2023年2月,中国Chiplet产业联盟联合国内系统、IP、封装厂商一起,制定了《芯粒互联接口标准》ACC1.0及《车规级芯粒互联接口标准》ACC_RV 1.0。该标准为高速串口标准,着重基于国内封装及基板供应链进行优化,以成本可控及商业合理性为核心导向,为提升国产高性能计算芯片的自主可控度奠定了坚实的基础。

(校对/赵月)