课题背景

芯片功耗密度的指数式暴增严重阻碍晶体管物理尺寸的缩微和集成度的提高。超低功耗CMOS场效应晶体管是实现高能效集成电路芯片的关键。亚阈值摆幅SS作为MOS晶体管的重要参数,其缩减可有效降低静态功耗和动态功耗,优化系统能效。依据载流子热激发的输运机理,SS参数受玻尔兹曼统计分布的影响,在室温下不能低于60 mV/dec(即著名的“玻尔兹曼限制”)。而随着晶体管栅长的缩微化,短沟道效应得到增强,亚阈值摆幅将进一步恶化。这也是电源电压调整、漏电控制以及最终功耗的主要限制因素。针对该科学问题,国内外研究学者相继提出新型陡峭摆幅器件概念,但亚阈值摆幅均无法接近理想值。因此,探索亚阈值摆幅极限,实现具有超陡切换特性的理想MOS开关晶体管是长期困扰国际学术界、产业界的命题。

研究内容

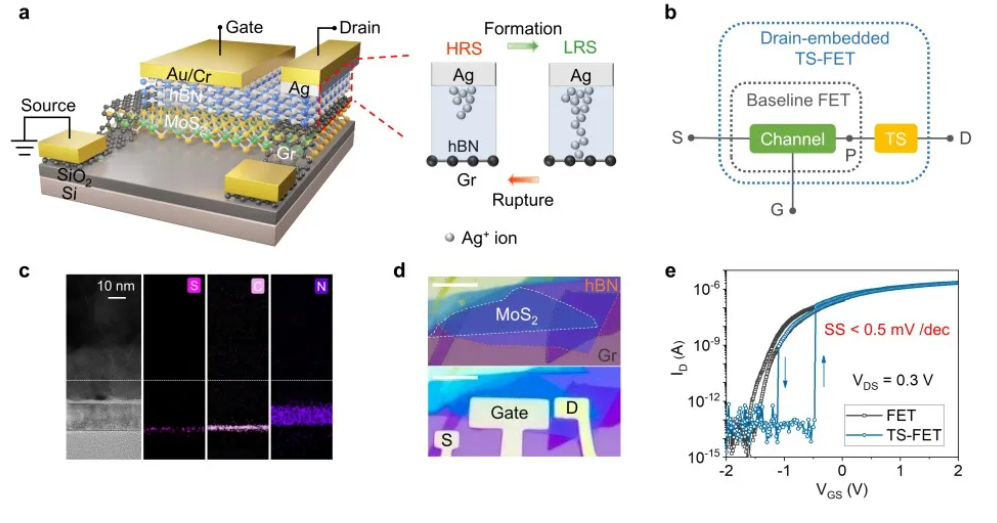

近日,浙江大学集成电路学院俞滨教授、徐杨教授、张亦舒研究员合作团队,提出一种全二维材料范德瓦尔斯异质结构(vdW)的晶体管,整合多种工作机制实现协同配合,利用功能材料(MoS2、hBN、Gr)的集群行为实现 “无亚阈值”工作,使得晶体管能够直接从关断状态切换到导通状态,完全消除了亚阈值区域,表现出一个理想逻辑开关的电学特性。该工作以题为“All-2D-Materials Subthreshold-Free Field-Effect Transistor with Near-Ideal Switching Slope”发表于ACS Nano(https://doi.org/10.1021/acsnano.4c03856)。本文第一作者为浙江大学集成电路学院博士生胡加杨和李涵茜。该工作得到了国家自然科学基金和省自然科学基金重大项目(创新群体)的资助。

课题亮点

通过在全二维材料vdW异质结构上集成忆阻器(阈值开关)和场效应沟道,展示了逻辑晶体管的近理想开关行为,表现为接近零的开关斜率(~0.33 mV/dec)、大开/关电流比(~107)和超低关态电流(~0.1 pA)。该晶体管可以在无亚阈值模式下工作,这归功于可调导通电压以及阈值开关超陡阻变特性,消除了亚阈值区域,克服MOSFET中60 mV/dec的玻尔兹曼热离子限制。该工作还系统地分析了CMOS反相器的开关动态特性,证明了由于无亚阈值操作而降低的动态/静态功耗。此外还制备了晶圆级晶体管阵列。虽然提出的无亚阈值晶体管是通过集成vdW二维材料来演示的,但这一概念的多功能性也反映在可替代沟道和阈值开关材料的选择上,未来有可能在硅基CMOS芯片得到推广应用。

俞滨

浙江大学集成电路学院教授

加州大学柏克莱分校电子工程博士、微纳电子学专家,浙江大学教授/博导,浙江大学国际科创中心战略科学家、未来科学研究院院长,NAI Fellow,IEEE Fellow,荣获IEEE杰出讲座奖和IBM学者奖。研究方向为类脑感知与计算、后摩尔电子学、新一代信息器件、先进微纳集成芯片等。学术经历包括斯坦福大学顾问教授、北京大学客座教授等。在硅基/碳基/低维半导体电子学、新型逻辑/存储器件、碳基互联、纳米传感、二维材料/异质结、微纳智造等领域做出多项原创性成果,发表包括 Nature Electronics、Nature Communications、Science Advances、Matter、Chemical Reviews、Advanced Materials、ACS Nano、IEEE旗舰期刊、IEDM、VLSI Symposium 等顶级国际会议在内300多篇论文,其中4篇入选期刊封面或Highlights。作为众多微纳电子器件和微纳加工技术的发明人,拥有300多项国际发明专利,在微纳电子学领域取得多项世界记录,在IEDM、VLSI Symposium等顶尖国际会议发表论文十余篇,包括全球首个10纳米双栅三维晶体管FinFET(FinFET目前为产业界集成电路芯片主流技术),由于在集成电路缩微化方面的杰出贡献,于2007年当选为IEEE Fellow。受邀在全球高校、企业、国际学术会议做180多场主旨/特邀报告,受聘国际半导体技术路线图(ITRS, 全球半导体产业15年战略技术规划)起草委员会,IEEE EDS和IEEE NTC 执委会,IEEE Fellow评委,IEEE George Smith奖评委,IEEE IEDM技术委员会Chair,IEEE EDL、IEEE T-NANO、IEEE T-ED、Nano-Micro Letters等学术期刊副主编/编辑/特邀编辑,斯坦福大学研究生课程特邀讲员,以及数十个国际学术会议顾问/组委/技术委员会Chair、Co-Chair和成员。

文章来源:浙江大学集成电路学院

评论

文明上网理性发言,请遵守新闻评论服务协议

登录参与评论

0/1000