(2024年12月5日,四川成都)英诺达(成都)电子科技有限公司隆重推出两款全新的静态验证EDA工具:EnAltius®CDC跨域检查工具和Lint RTL代码检查工具。这两款工具的推出,将进一步提升芯片设计的效率和可靠性,助力中国芯片产业的发展。

静态验证是通过分析设计的源代码来发现设计中的问题,作为业界普遍使用的方法,在设计中通过配合动态仿真验证和形式化验证,可以显著提高验证的覆盖率,帮助设计师在设计开发的早期更快地发现和诊断设计缺陷,从而缩短设计验证所需的时间。这两款工具的发布进一步丰富了英诺达的产品线,迄今为止英诺达已经推出了6款面向数字电路的静态验证和分析EDA工具。

新产品概览

EnAltius®昂屹®CDC 跨域检查工具

跨时钟域(Clock Domain Crossing)是数字集成电路设计中常见的复杂问题,时钟域处理不当通常会出现亚稳态、数据丢失、潜在毛刺、多数据相关性丢失等问题,导致芯片功能异常甚至失效,是流片失败的主要因素之一。EnAltius®CDC可以在保证跨时钟域CDC检查完备性和准确性的同时,在最短时间内向用户提供简洁的违例报告。其专有的静态逻辑检测算法,能够准确解析跨时钟域经典结构,还可以通过电路功能性分析从而完成难度更高的非经典的跨时钟域结构分析,为用户提供全面而精确的分析结果。及早发现并解决CDC问题,可以大大提高芯片的可靠性,减少芯片在实际应用中发生故障的概率,而且在芯片设计早期发现并修复CDC问题,可以降低设计迭代成本。

EnAltius®昂屹®Lint RTL代码检查工具

Lint工具是代码工程师的左膀右臂,能够发现设计代码中潜在的语法错误和逻辑错误,尤其是在设计中对IP、模块等进行复用时,经常出现风格不统一,不利于维护的问题。对于这些问题,设计团队要在第一时间解决,否则将直接导致编译或运行错误,影响开发效率和质量。EnAltius®Lint不仅可以提供基本语法、语义和规范检查,还可以检测在仿真、验证或综合阶段的潜在缺陷,帮助设计团队实现检查的“左移”,从而实现早期RTL代码质量签核。该工具采用业界广泛应用的编码规范,例如RMM和STARC,以及英诺达及其设计合作伙伴在该领域多年的专业积累而成的规范。这款工具不仅能提高代码的可读性,便于团队协作,还可以降低设计风险,提高芯片的可靠性。

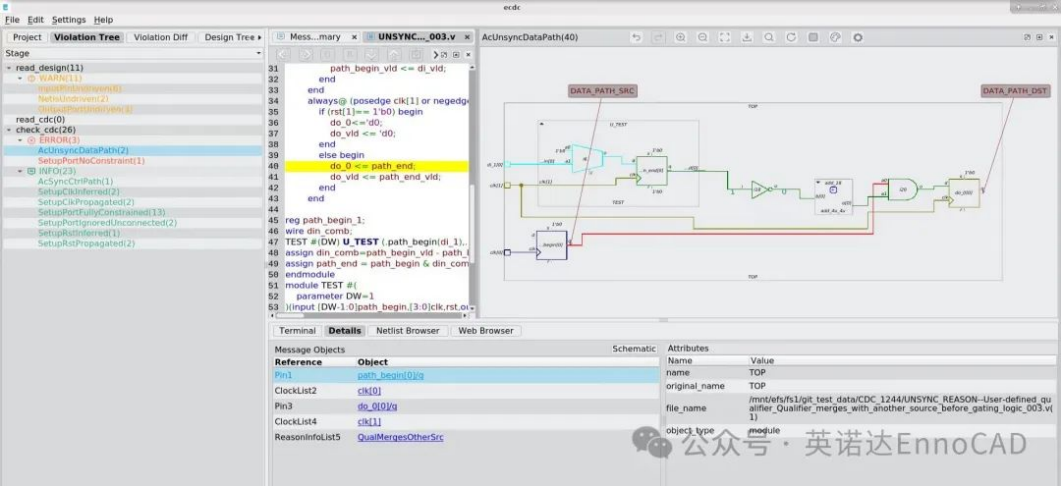

ECDC工具的GUI界面

这两款工具均基于英诺达全新的软件架构,通过读入标准文件格式进行分析和报告。同类工具的违规报告往往存在大量重复和组织混乱的信息,增加了分析难度。EnAltius®CDC和Lint工具对同源违例进行合并,并对消息进行了归类,减少了重复的分析、调试和迭代过程。即使在设计异常庞大的情况下,该工具以目标为导向的简洁报告和组织功能依然可以帮助用户聚焦关键问题。

此外,通过图形化用户界面(GUI),从违例信息开始,到违例路径到电路细节,该工具为用户清晰地展示电路中的潜在问题。用户可以通过RTL源代码或电路原理图进行追根溯源,并精准定位到问题源头。其中,增量电路原理图仅仅显示违例相关逻辑,将任何不相关逻辑隔离开,为用户排除干扰信息从而能够轻松地深入分析复杂设计。

华中科技大学集成电路学院童乔凌教授表示:“英诺达的静态验证工具让我们在设计早期就发现了许多我们以前没有注意到的问题,大大提高了芯片的可靠性,让我们对代码的质量有了更高的信心。该系列工具也加速了我们的设计迭代,提升了效率。期待英诺达能够持续创新,推出更多先进的EDA工具,为中国芯片产业的发展贡献更大的力量。”

“随着芯片设计复杂度的不断提高,设计企业对静态验证工具的需求也越来越迫切。”英诺达的创始人、CEO王琦博士表示,“特别是诸如CDC和RTL代码质量检测这类基础且不可或缺的验证工具,市场当前对国产化的解决方案抱有极大的期待与需求。英诺达全新发布的EnAltius®CDC和Lint这两款工具,将为芯片设计企业提供更加高效、可靠的静态验证解决方案,助力其在激烈的市场竞争中保持领先优势。”

12月11-12日,英诺达将亮相在上海举办的第三十届集成电路设计业展览会(ICCAD-Expo),英诺达将携最新产品参会,您可以关注我们的演讲信息,或前往英诺达的展台了解我们的系列EDA工具。