模拟芯片是我国集成电路产品的重要基石,是国家安全保障和高质量发展不可或缺的重要基础支撑。在技术进步和市场需求的双重推动下,模拟芯片在多个领域展现出巨大的发展潜力和应用价值。同时,面对国内外的挑战,加强自主创新和推动国产化进程也是未来模拟芯片创新体系发展的重要方向。复旦大学RFiCAE课题组在闫娜教授、许灏青年研究员的指导下,在低功耗无线通信收发芯片、宽带射频收发芯片、高性能锁相环、高速模数/数模转换器、高能效混合信号芯片设计等方面取得了一系列的研究成果,发表于IEEE JSSC、IEEE TCAS-I、IEEE TMTT、IEEE ISSCC/RFIC/CICC/ESSERC等国际著名期刊会议上。

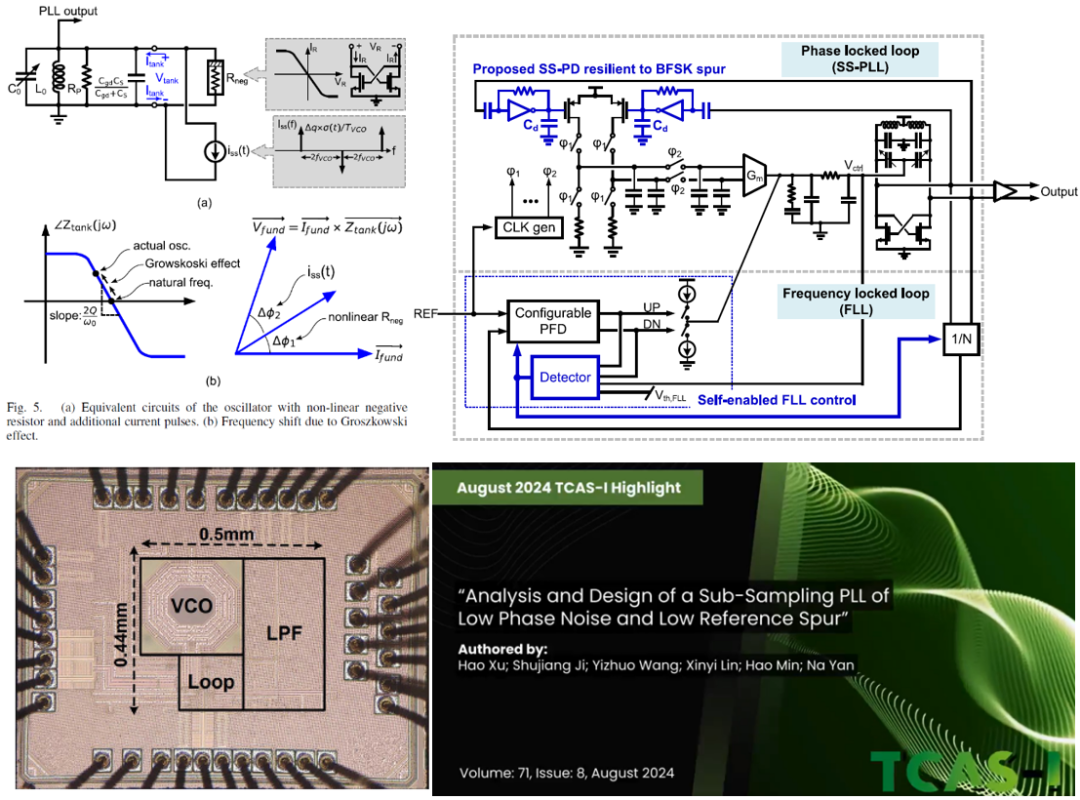

1. 亚采样型锁相环杂散机理研究和杂散噪声抑制技术

亚采样鉴相器对压控振荡器周期性的干扰是限制亚采样型锁相环杂散的主要来源,针对这一问题,研究团队建立了亚采样鉴相器对压控振荡器的非线性调制效应模型,提出了一种嵌入线性电容的级联式高隔离度相位检测器,实现了对锁相环输出杂散和噪声的同时抑制;针对亚采样型锁相环中频率锁定环路消耗功耗较高的限制,团队提出一种可以实时监测环路锁定状态的自启动频率锁定环路,大幅降低了芯片功耗。最终在40nm CMOS工艺下实现一颗2.4GHz输出、185fs积分抖动、-72dBc杂散、1.1mW功耗的锁相环芯片,成果发表在2024年IEEE Transactions on Circuits and Systems – I: Regular Papers (TCAS-I),获评2024年8月亮点论文。

论文由微电子学院青年研究员许灏和博士研究生纪书江等同学共同完成,论文第一作者是许灏,通信作者是闫娜。

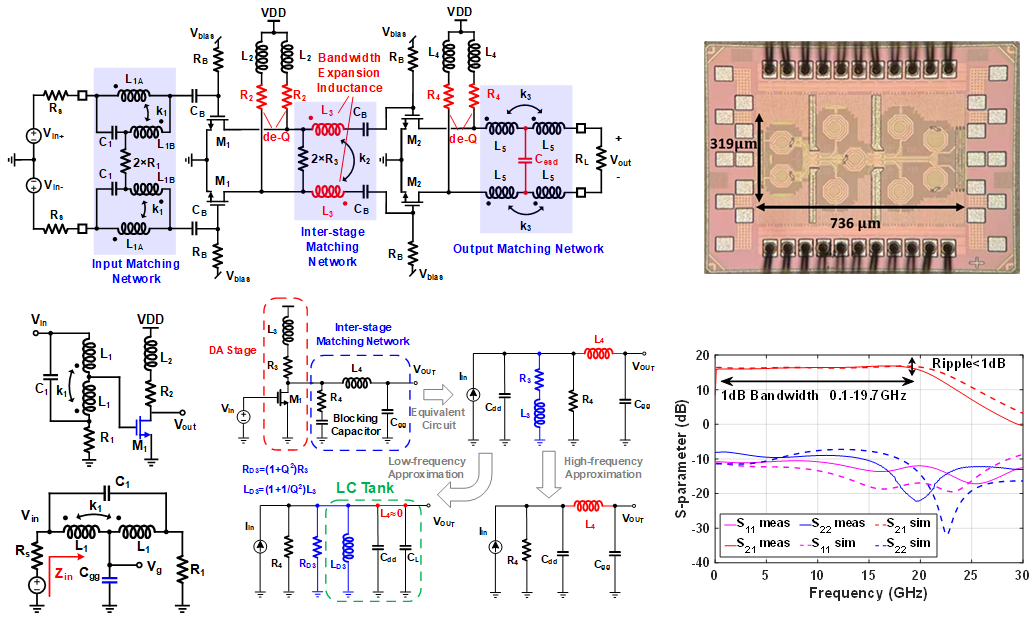

2. 0.1-19.7GHz宽频带覆盖功率放大器

研究团队提出了一种基于LC谐振网络的两级超宽带低纹波功率放大器(PA),同时解决了传统窄带匹配网络带宽受限和传统分布式放大器面积过大的问题。基于T-coil匹配网络,突破性地将输入寄生电容在宽带内实现了谐振,使得所提出的PA在整个频段内实现了良好的输入匹配。通过在级间和输出匹配网络采用带宽拓展技术,打破了传统功率放大器带宽限制。同时基于峰值频率错位调谐方案,解耦了带宽与增益纹波的相互制约,从而实现了超宽带下的超低增益纹波。该PA基于28nm CMOS工艺制造,在0.1-19.7GHz的超宽带应用下实现了±0.5dB的增益纹波。所提出的PA在整个频段内实现了小于11dB的回波损耗,15.8-16.8dB的增益,9.1-11.6dBm的饱和输出功率以及3.9-7.7%的PAE。

相关成果发表在集成电路顶级会议2024 IEEE ESSERC,复旦大学微电子学院博士生孙安为第一作者。

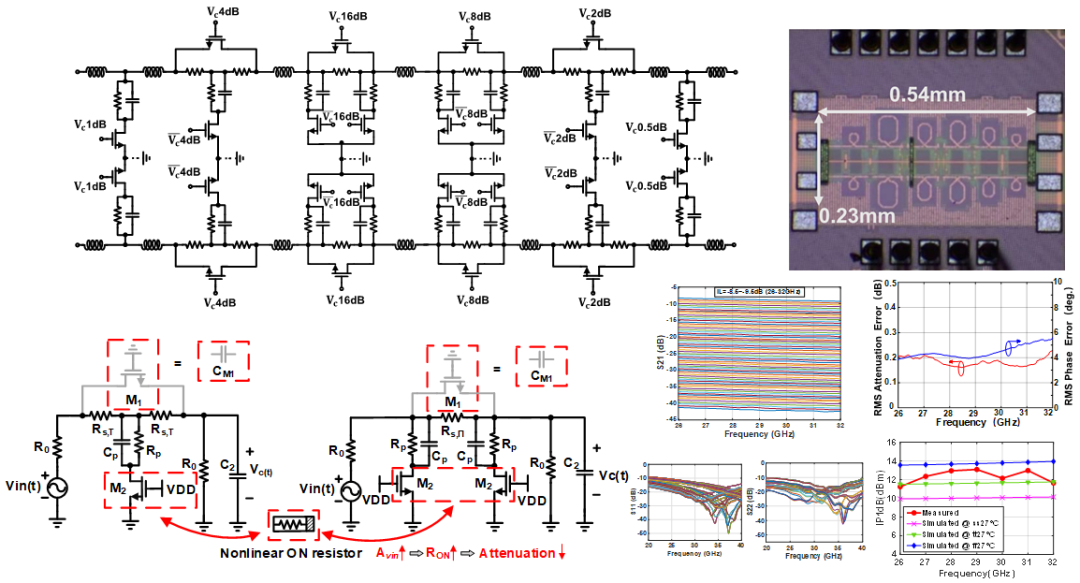

3. 26-32GHz高精度高线性度衰减器

研究团队提出了一种基于并联电容相位补偿技术的衰减器,通过对电路的传递函数进行详细分析,该设计所引入补偿电容实现了零极点抵消,从而在宽带范围内降低了相位和衰减误差。本设计通过对串联支路开关尺寸和并联支路的阻抗比例的量化分析与优化设计,阐明了插入损耗,带宽和线性度的相互限制,提出了能够快速收敛最优指标边界的设计方法,大大减小了设计所需迭代时间。同时,团队基于EKV模型,分析了衰减器单元的线性度,并提出了优化的衰减器单元的级联顺序,突破了传统CMOS衰减器线性度差的难题。所设计的衰减器采用40nm CMOS工艺制造,在26-32GHz的带宽内实现了以0.5dB为步进的0-31.5dB的衰减范围。该衰减器在紧凑的面积(0.124mm²)内实现了小于0.23dB/5.58°的RMS衰减/相位误差以及大于11.2dBm的IP1dB。

相关成果发表在集成电路顶级期刊IEEE TMTT,复旦大学微电子学院博士生孙安为第一作者。

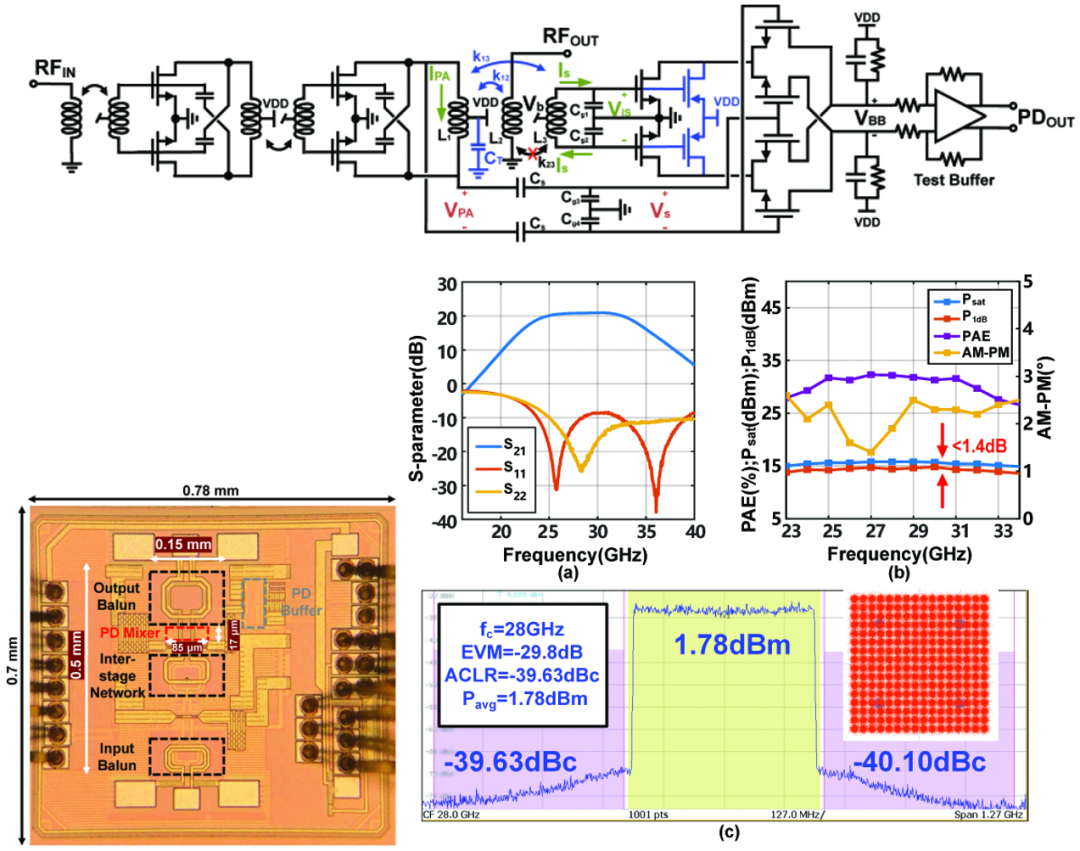

4. 集成功率检测的25-31GHz功率放大器

研究团队基于自混频架构,提出了一款紧凑型的高性能功率检测器。通过优化耦合端口位置,实现了单端功率输出下的差分电压、电流检测,避免了额外的单转差巴伦带来的面积开销。此外,通过传递函数的量化分析,提出了一种不依赖外部移相单元的内生相位补偿方式,保证了负载失配情况下准确的功率检测。在自混频器的设计当中则采用了电流抽取技术,优化了混频器的低频闪烁噪声,提高了整体动态范围。结合以上技术,团队设计了一款面向Ka波段卫星通信的小面积、高动态范围、抗电压驻波比、非侵入式功率检测器,并集成于毫米波功率放大器中。该功率检测器在25~31GHz的范围内可实现大于33dB的动态范围;当负载端电压驻波比为2:1/3:1时,频段内功率检测误差分别小于±1.5dB/±3.8dB;功率检测器核心面积仅有3520μm2。

相关成果发表在2024 IEEE RFIC会议上,复旦大学微电子学院硕士生秦昊祺、博士生顾俊杰为共同第一作者。

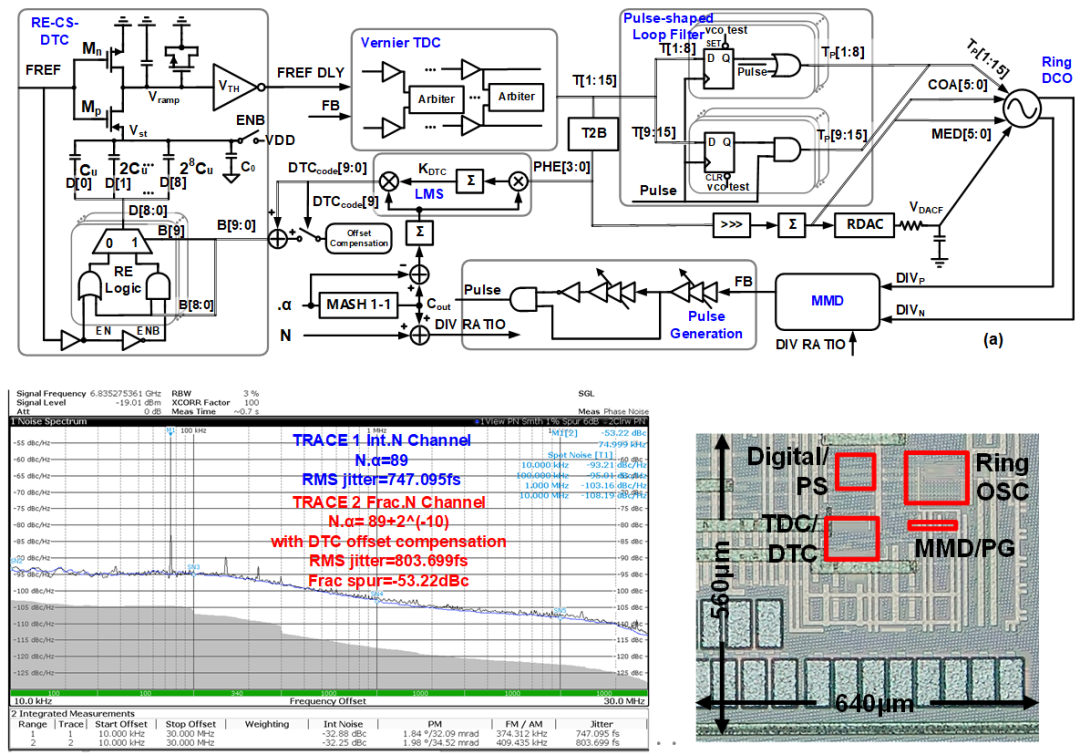

5. 基于脉冲整形和环形振荡器的极小面积锁相环

研究团队提出了一种基于脉冲整形的大环路带宽锁相环(PLL)。与LC型振荡器相比,环形振荡器虽然在面积上具有优势,但其相位噪声表现较差。为解决这一问题,采用脉冲整形技术提升了锁相环的环路带宽,突破了传统锁相环环路带宽不能超过参考时钟频率10%的限制。为了消除小数分频带来的DSM噪声,设计中采用了量程扩展型恒定斜率数字时间转换器,在电容阵列面积不变的情况下,有效增加了数字时间转换器的量程。同时,结合有效沟道长度调制效应和可变负载电容效应,进一步提升了数字时间转换器的线性度。该锁相环基于28nm CMOS工艺实现,在6.8GHz频率下,展现出小数10kHz至30MHz的积分噪声为803.7fs,整数边界杂散为-53dBc,核心面积为0.025mm²,FoMjitter-N-Area为-269.9,能效为0.83mW/GHz。

相关成果发表在2024 IEEE ESSERC会议上,复旦大学微电子学院博士生高皓原为第一作者。

6. 5-18GHz宽频带覆盖正交无线接收机

研究团队提出了一款能够应用于6G通信频段的超宽带低噪声可重构射频接收机。在传统的接收机架构中,通常使用一个公共的跨导单元驱动I-Q两通道的混频器,这使得传统接收机需要使用25%占空比的非交叠时钟进行下变频,而高频应用下非交叠时钟的产生是十分困难的;同时非理想的时钟交叠会恶化接收机输出的I-Q失配。针对这个问题,研究团队提出了一款I-Q通道隔离度提升的正交下变频接收机结构,通过在I-Q通路引入独立的跨导单元电路,阻止了I-Q通路之间的馈通,同时使得接收机能够使用50%占空比的时钟进行下变频,简化了时钟产生电路的设计。此外,为了提升模拟基带电路的线性度,

该接收机在模拟基带电路中引入了无源滤波器,在降低功耗的同时提升了整体接收机的线性度。该接收机基于28nm CMOS工艺制造,在104-199mW功耗下,实现了5-18GHz频带覆盖范围、100-500MHz的连续可调基带带宽、40dB的增益可调范围以及2.1-5.4dB的噪声系数。

该接收机芯片由复旦大学微电子学院青年研究员许灏与博士生毕俊彦、邹滕浩和何伟韬等同学共同完成,相关成果发表在集成电路设计领域顶级会议2024 ISSCC与顶级期刊 2024 IEEE JSSC。

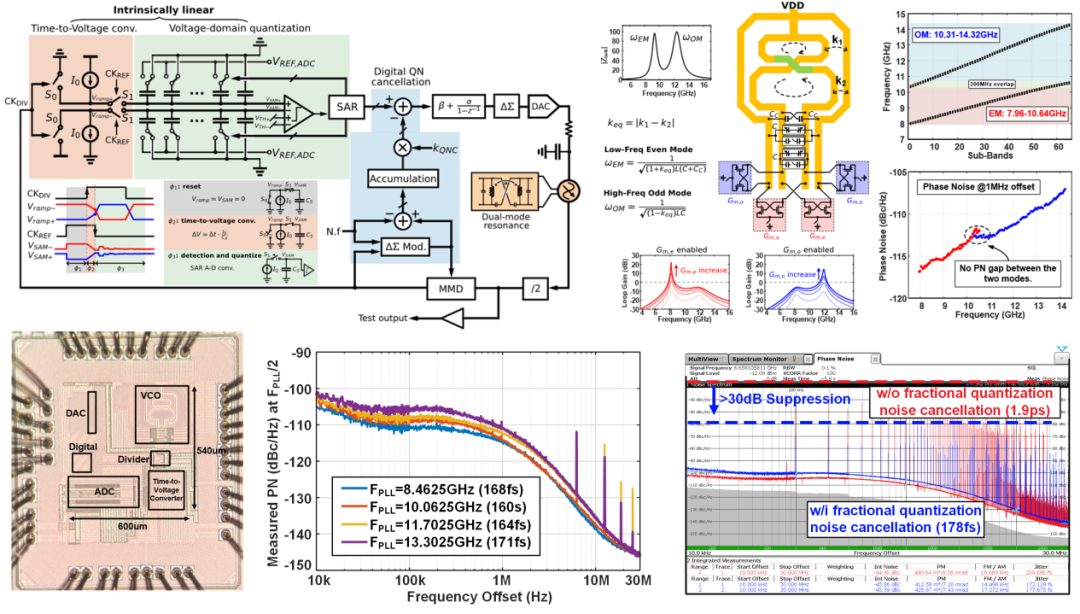

7.采用ADC全域量化的8-14GHz宽带小数分频锁相环

研究团队提出了一种基于模拟数字转换器(ADC)鉴相的低噪声低杂散的小数分频型全数字锁相环(Frac-N ADPLL)。针对传统小数型锁相环带内噪声抑制和小数杂散消除的难题,提出了一种基于线性时间-电压转换器和模拟数字转换器的高增益高线性度高动态范围的鉴相器,并提出一种全数字域小数量化噪声消除的技术。所提出鉴相器的固有线性转换特性消除了噪声折叠并减小了小数杂散,避免了复杂的线性度校准电路,实现了低噪声和低杂散的小数频率综合。该锁相环芯片采用40nm CMOS工艺实现,以20mW的功耗实现8~14GHz的宽带频率综合,整数模式和小数模式下的积分抖动分别小于160fs以及180fs,带内(100kHz频偏)小数杂散水平低于-57dBc。

相关成果发表于国际集成电路顶级会议2024 IEEE CICC,复旦大学微电子学院博士生王一卓为第一作者。

文章来源:复旦大学微电子学院