2025年2月16日至20日,第72届ISSCC(国际固态电路会议)在美国旧金山召开,模拟集成电路重点实验室作为第一署名单位在ISSCC 2025发表了4篇学术论文,此为西安电子科技大学作为第一署名单位首批被ISSCC接收的论文。所涉及研究内容包括高速串行数据接口芯片、频率综合器与串联谐振振荡器、高速高精度模数转换器、MEMS传感器接口芯片等。国家海外高层次青年人才赵潇腾、博士后王凌带队参加了ISSCC会议。

ISSCC(International Solid-State Circuits Conference)国际固态电路会议始于1953年,是全球学术界和工业界公认的集成电路设计领域最高级别会议之一。ISSCC通常是各个时期国际上最尖端集成电路技术最先发表之地,每年吸引超过数千名来自世界各地工业界和学术界的参会者。

图1. 模拟集成电路重点实验室的ISSCC 2025参会人员

论文一

论文一 7.8 A Reference-less CDR Using SAR-Based Frequency-Acquisition Technique Achieving 55ns Constant Band-Searching Time and up to 63.64Gb/s/μs Acquisition Speed

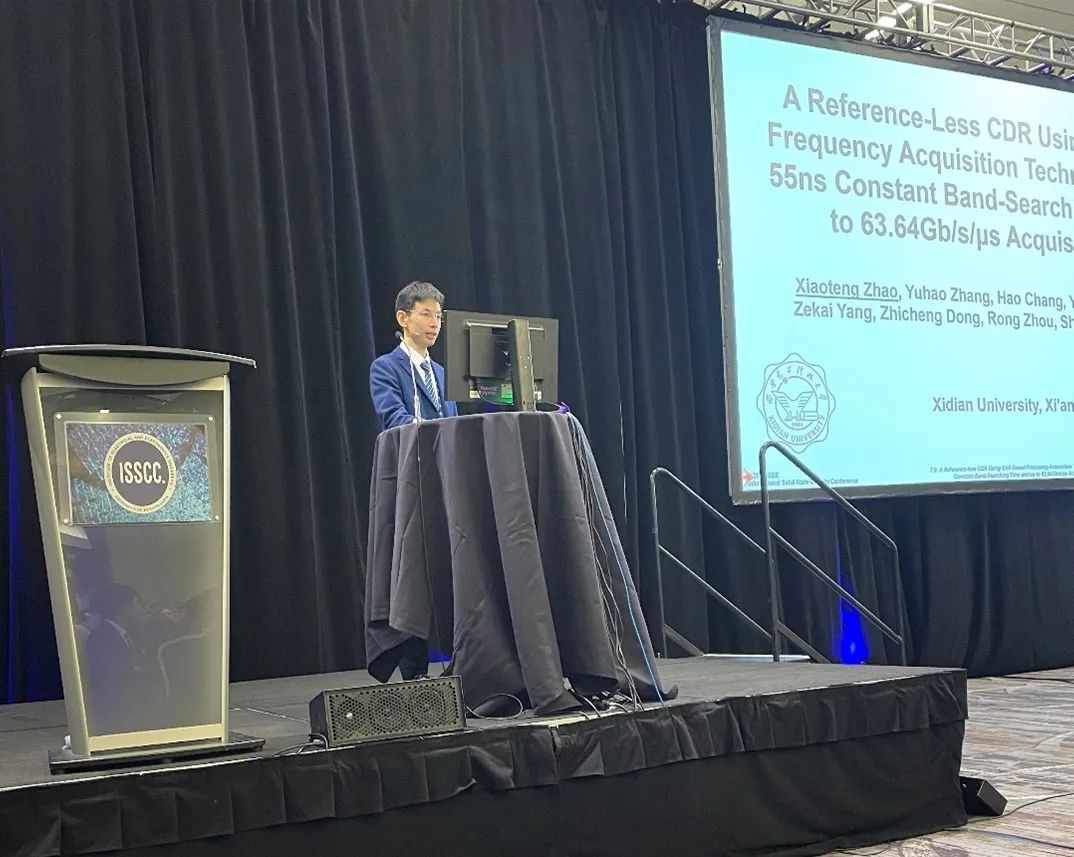

图2 赵潇腾教授报告论文7.8

面向数据链路中出现的频繁休眠与唤醒,实验室为实现链路的快速建立提出了一种超快锁定的无参考时钟与数据恢复电路。该工作提出了一种基于逐次渐进比较(SAR)的频率捕获方法。通过识别“慢”信号得到频率差极性。所提出的时钟数据恢复电路仅需55ns的恒定频带切换时间,在此过程中实现了高达63.64 Gb/s/μs的频率捕获速度,与可查阅参考文献对比,实现了当前无参考频率捕获的最快速度。借助所提出的净电流的电荷泵,实现了小于150ns的总捕获时间,比已有的研究工作至少缩短了4倍。

该工作以"A Reference-less CDR Using SAR-Based Frequency-Acquisition Technique Achieving 55ns Constant Band-Searching Time and up to 63.64Gb/s/μs Acquisition Speed"为题,发表于2025年 ISSCC的 超高速有线通信(Ultra-High-Speed Wireline)分会场。该文章第一作者及演讲者为西安电子科技大学赵潇腾教授,第一学生作者为章宇浩博士研究生,通讯作者为西安电子科技大学朱樟明教授和刘术彬教授。

论文二

论文二 19.11 A 13GHz Charge-Pump PLL Achieving 15.8fs rms Integrated Jitter and -98.5dBc Reference Spur

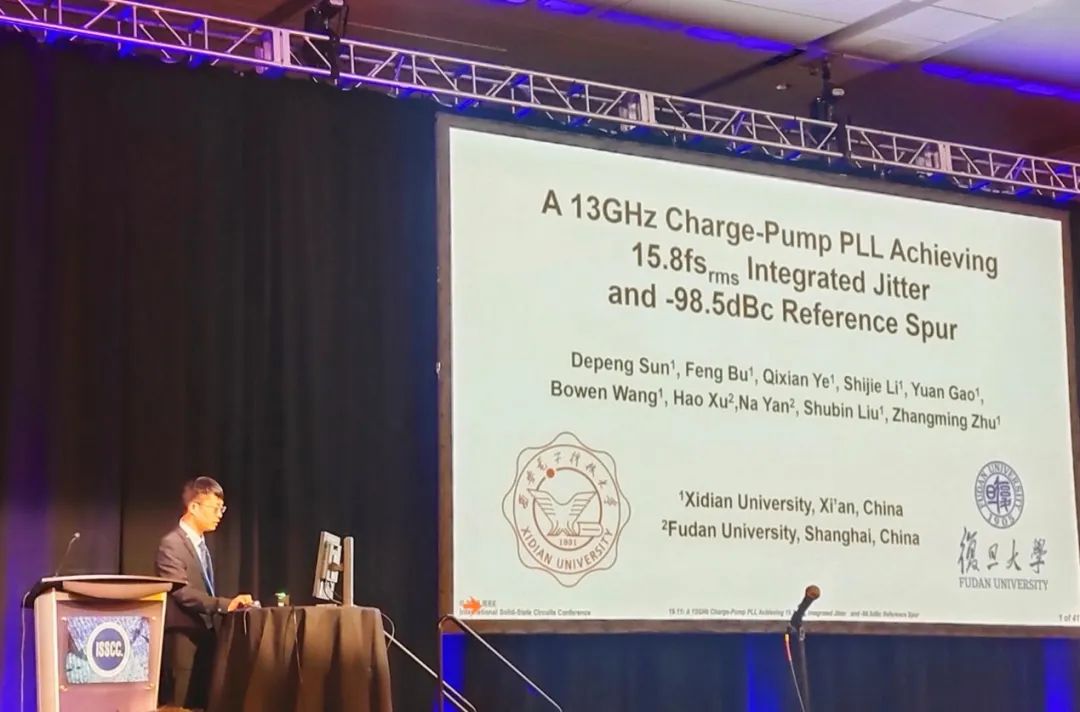

图3 步枫博士生报告论文19.11

面向通信系统高速率数据传输需求,实验室针对本地频率源提出一种极低抖动、低杂散的锁相环时钟电路。通过提出的电阻放电型时间放大器,显著降低了PFD自身噪声,并提高对后级电路噪声的抑制。此外,针对传统串联谐振压控振荡器的过压问题,提出的电容分压技术成功降低了有源器件的振荡幅度,在保证性能的同时,大幅提升了电路的可靠性。最后,通过提出的开关采样滤波器技术,解决了电荷泵失配带来的杂散影响。该工作在13GHz输出频率下,实现了15.8fs的积分抖动和-98.5dBc的参考杂散。在目前国际上已报道的锁相环中,该工作实现了最优的积分抖动。

该工作以“A 13GHz Charge-Pump PLL Achieving 15.8fsrms Integrated Jitter and -98.5dBc Reference Spur”为题,发表于2025年ISSCC的频率综合器和串联谐振压控振荡器(Frequency Synthesizers and Series-Resonance VCOs)分会场。该论文第一作者为西安电子科技大学孙德鹏副教授,通讯作者为西安电子科技大学刘术彬教授,文章由第一学生作者步枫博士研究生进行演讲汇报。

论文三

论文三 24.2 A 14b 1GS/s Single-Channel Pipelined ADC with a Parallel-Operation SAR Sub-Quantizer and a Dynamic-Deadzone Ring Amplifier.

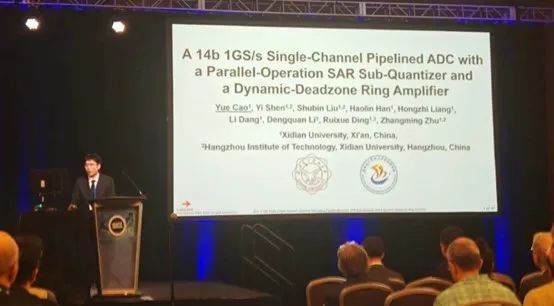

图4 曹越博士生报告论文24.2

面向通信系统应用,实验室提出了一款14位1GS/s模数转换器。该工作提出了一种并行量化技术与一种动态死区环形放大器。不同于现有流水线架构的串行时序,并行量化技术使余量转换和余量放大同时进行,在不降低模数转换器采样率前提下,分配了足够的时间给余量放大和转换,提升了整体能效。该工作在1GS/s采样率下,奈奎斯特输入频率时,实现了85.8dB的SFDR和68.2dB的SNDR。在目前已报道的ISSCC和VLSI会议上采样率≥0.5GS/s的高速模数转换器中,该工作实现了最高的性能优值FOMs(173.3dB)。

该工作以 " A 14b 1GS/s Single-Channel Pipelined ADC with a Parallel-Operation SAR Sub-Quantizer and a Dynamic-Deadzone Ring Amplifier "为题,发表于2025年 ISSCC的高频ADC (High-Frequency ADCs)分会场。该文章第一作者及演讲者为西安电子科技大学博士研究生曹越,通讯作者为西安电子科技大学朱樟明教授和沈易教授。

论文四

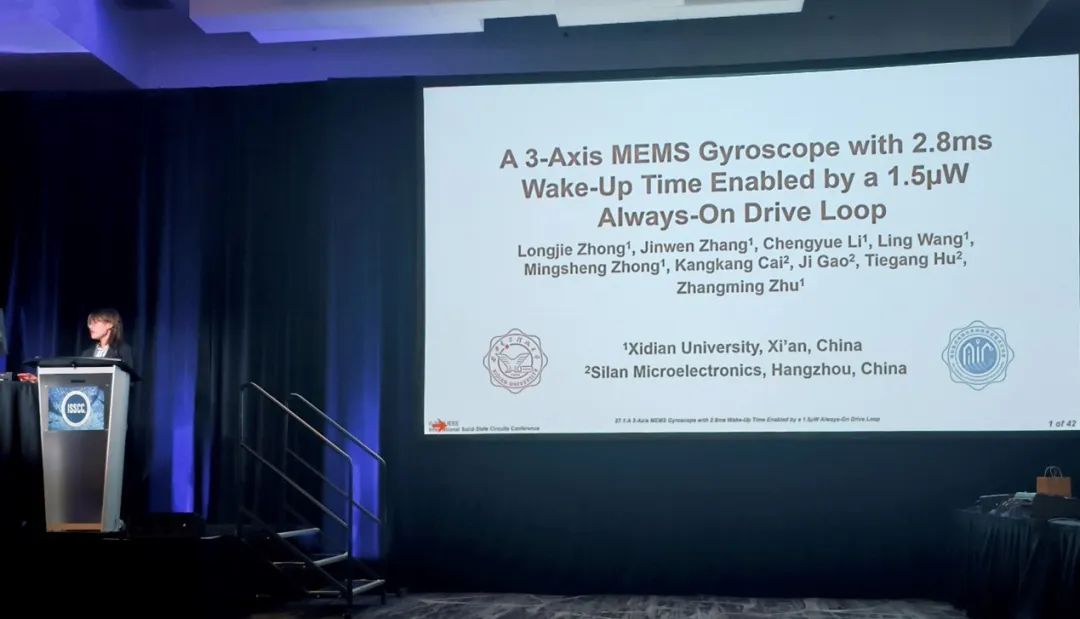

论文四 27.1 A 3-Axis MEMS Gyroscope with 2.8ms Wake-Up Time Enabled by a 1.5µW Always-On Drive Loop

图5 王凌博士后报告论文27.1

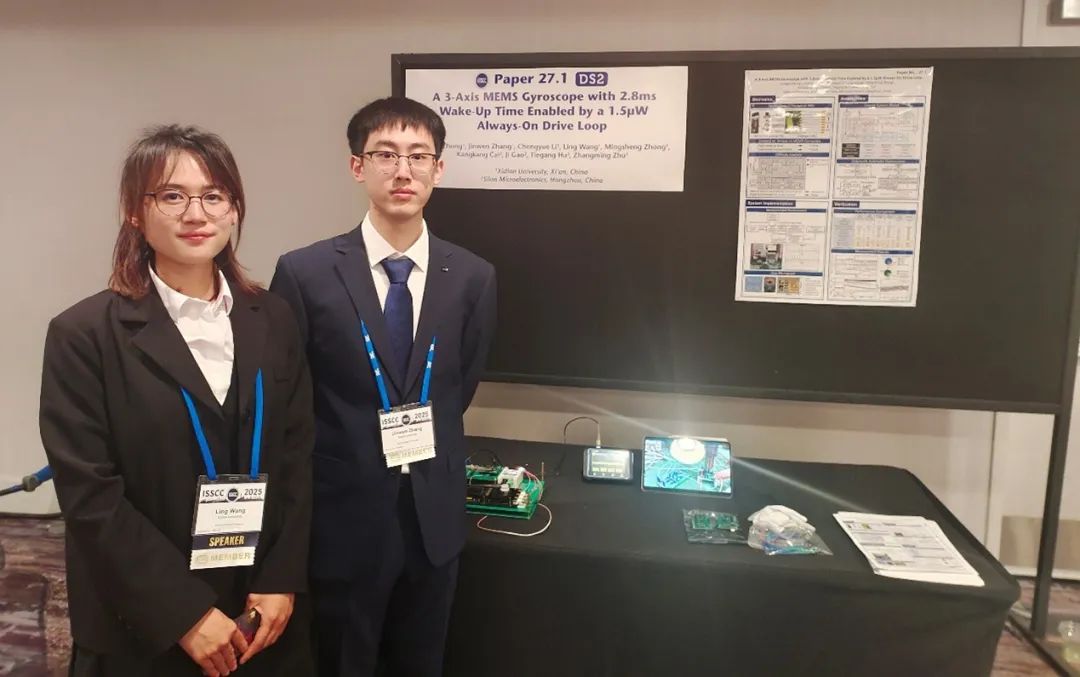

图6 王凌博士后与张锦文硕士生现场演示论文27.1

面向MEMS陀螺仪的事件驱动应用需求,针对常开功耗与唤醒时间约束,实验室提出了一种基于占空比自动寻优突发模式锁相环的常开驱动接口电路。通过基于bang-bang控制的自动动态占空比调节,实现1.5µW的常开功耗、2.8ms的唤醒时间和-40-85°C的宽温域的稳定工作,打破国际上常开功耗与唤醒时间指标记录,并首次实现了宽温度范围鲁棒的常开模式。该工作是和杭州士兰微电子股份有限公司共同完成的。

该工作以“A 3-Axis MEMS Gyroscope with 2.8ms Wake-Up Time Enabled by a 1.5µW Always-On Drive Loop”为题,发表于2025年ISSCC的传感器接口电路(Sensor Interfaces)分会场,作为第一篇文章报告,并在Demo Session 2分会场进行了现场展示。该文章第一作者为西安电子科技大学钟龙杰副教授,演讲者为王凌博士后,第一学生作者为张锦文硕士研究生,通讯作者为朱樟明教授。该工作获得了杭州士兰微电子股份有限公司的合作支持。

评论

文明上网理性发言,请遵守新闻评论服务协议

登录参与评论

0/1000