晶圆级系统大芯片理论与设计是指领域专用软硬件协同的复杂系统设计基础理论和晶圆级高密度集成的设计方法,以及在此基础上应用系统与晶圆级芯片的高效映射和部署方案。晶圆级系统大芯片是基于晶圆级高密度集成工艺创新和软硬件协同结构创新实现的面向特定领域专用的信息系统物理形态。具备超高集成密度与超灵活功能部署的晶圆级系统大芯片通常具有超高的功能密度。晶圆级系统大芯片摆脱了传统微电子技术对先进制程的依赖,可通过异构异质集成、多光罩拼接和晶圆级键合等方式实现系统摩尔定律的延续,并通过软件定义体系结构赋能集成电路设计与应用全流程,实现多应用场景垂直整合和随阅历数据的自我演化。目前,晶圆级系统大芯片理论与设计的研究成果保持着高速迭代,并快速渗透到云计算、超算、智算等大型信息系统基础设施中。

晶圆级系统大芯片理论与设计为提升信息系统性能、效能与处理能力提供了理论基础,其主要研究方向包括领域专用软硬件协同架构和晶圆级集成工艺。领域专用软硬件协同架构是指面向领域应用共性特征,在计算系统设计和运行全流程中,通过统一的描述和工具对软件架构与硬件架构进行集成开发,跨越软硬件界面进行系统优化,确保软硬件协同工作与高效交互,实现更高的系统性能和效率的计算架构设计范式。晶圆级集成工艺基于先进集成技术与微电子理论,研究晶圆级键合、跨尺度高精度集成等工艺技术,设计晶圆级系统大芯片的硬件系统。

晶圆级系统大芯片理论与设计未来发展仍需解决可靠性设计与测试、应用部署优化、生成式晶上互连网络、系统广义鲁棒性技术四方面问题。首先,晶圆级系统大芯片需要更可靠的设计与测试技术来保障硬件系统的生产良率和运行可靠性。其次,应用部署优化技术亟须进一步优化,以实现复杂应用到硬件系统的高效映射。再次,晶上互连网络的生成式结构可为未来智能计算系统提供晶圆级系统大芯片底座。最后,晶圆级系统大芯片的系统广义鲁棒性技术可为未来信息系统基础设施新形态提供安全支撑。

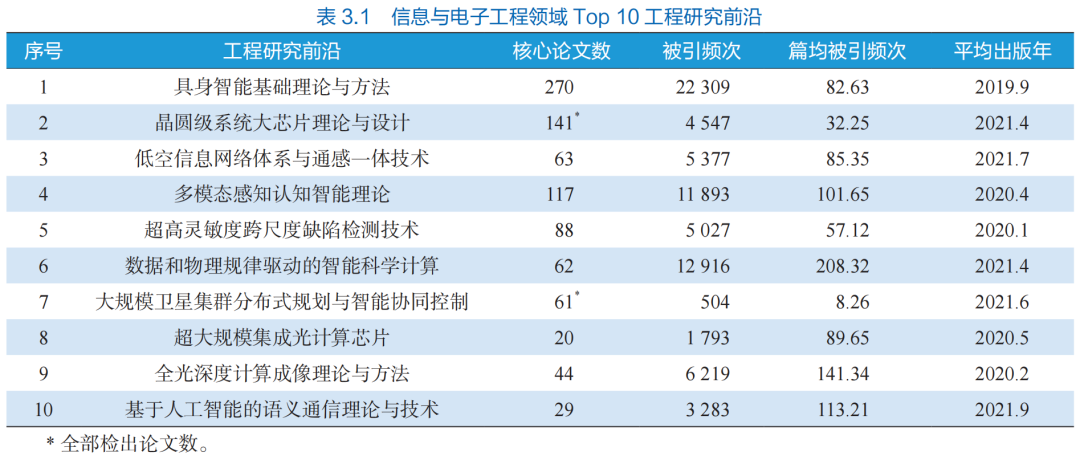

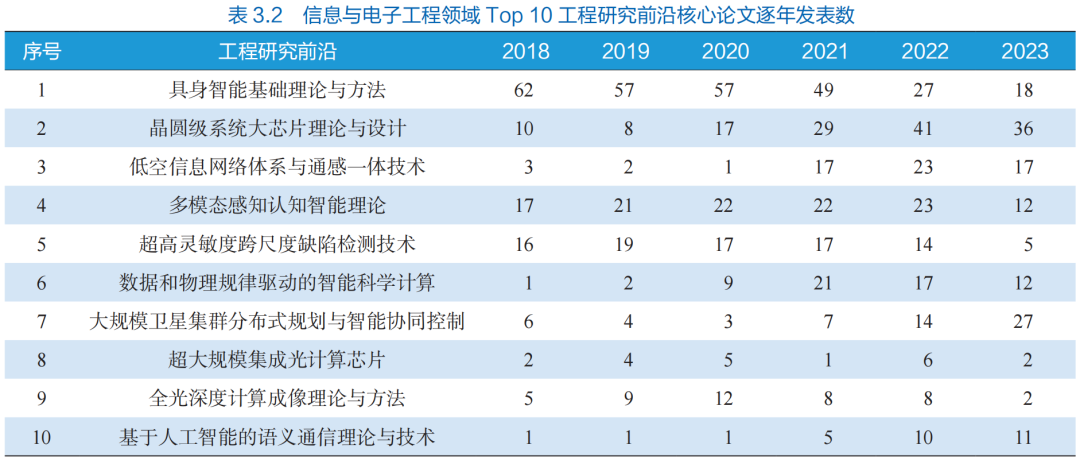

该前沿主题2018—2023年间发表的核心论文(注:针对该主题在Web of Science检索得到的被引频次位于前10%的高影响力论文——截至2023年12月)数量及其逐年发表情况见表3.1和表3.2。

晶圆级系统大芯片通过采用领域专用软硬件协同系统架构设计和晶圆级高密度集成方法的联合创新结构,实现领域内复杂应用到晶圆级系统大芯片硬件的映射,具有功能密度大、能效能重高、应用部署灵活等优点。然而,由于目前晶圆级系统大芯片资源规模大、结构复杂,且高度依赖先进集成工艺能力,芯粒之间功能协同难度大,晶圆级系统大芯片理论与设计亟须在理论架构和工艺实现两方面取得突破。

首先,在理论架构方面,主要呈现两大趋势。一是体系架构设计与应用任务深度融合。传统面向全领域应用的通算算力占比自2016年(95%)起逐步下降,预计到2030年将降至30%以下;而面向人工智能应用的智算算力占比则从2016年的3%迅速攀升,预计到2030年将达到70%以上。智能算力系统的体系架构设计一直与机器学习算法的演进紧密绑定并深度融合。二是软硬件协同,包括协同设计、协同仿真、协同运行与协同评估等。相比于通用计算系统软硬件解耦实现面向全领域计算一切可计算问题、专用计算系统软硬件一体实现面向专门应用最大限度提升性能与效能,软硬件协同在保持系统灵活性的基础上可实现计算综合能力的大幅提升。

其次,在工艺实现方面,一个重要的发展方向是晶圆级硅基板设计与实现工艺,旨在解决晶圆级互连硅基板的制备难题,进而提升异构集成系统的设计空间;另一个发展方向是高密度高精度集成工艺,需先突破异构异质芯粒到晶圆级硅基板的高密度键合工艺以及高密度晶圆级供电和散热工艺,再通过跨尺度高精度集成工艺实现晶圆、供电、散热等微系统到系统的可靠组装。这一方向的主要研究机构包括加州大学洛杉矶分校、伊利诺伊大学、台湾积体电路制造股份有限公司、清华大学、中国科学院微电子研究所、法国原子能委员会电子与信息技术实验室(CEA-Leti)等。

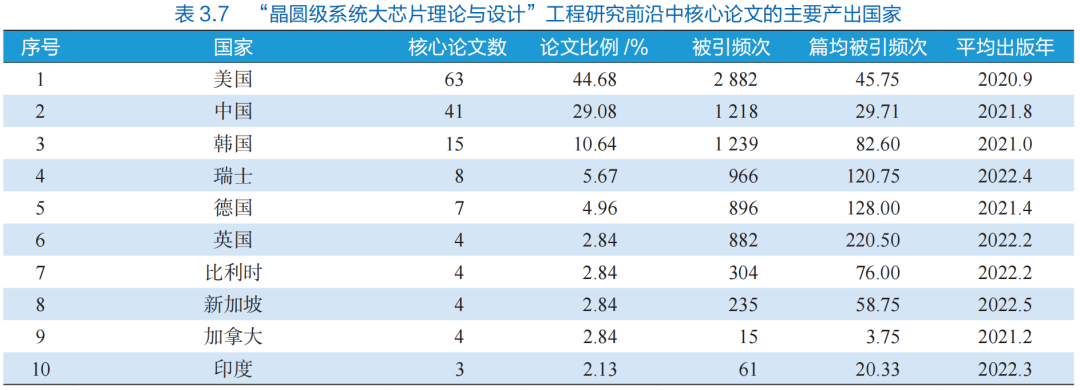

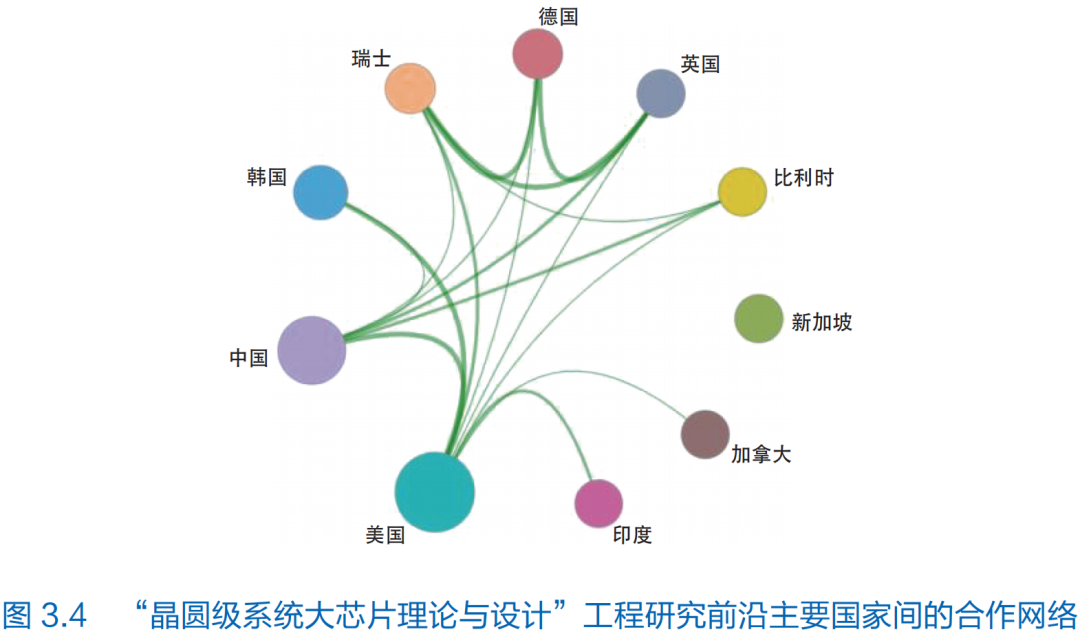

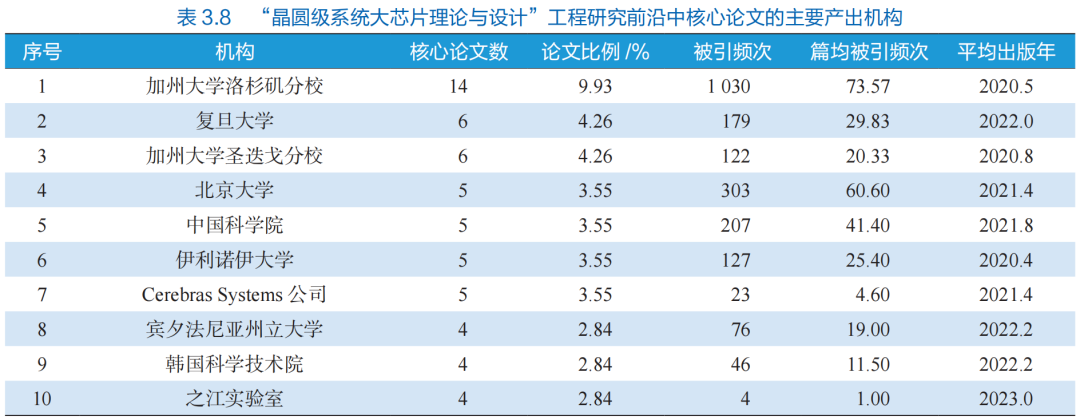

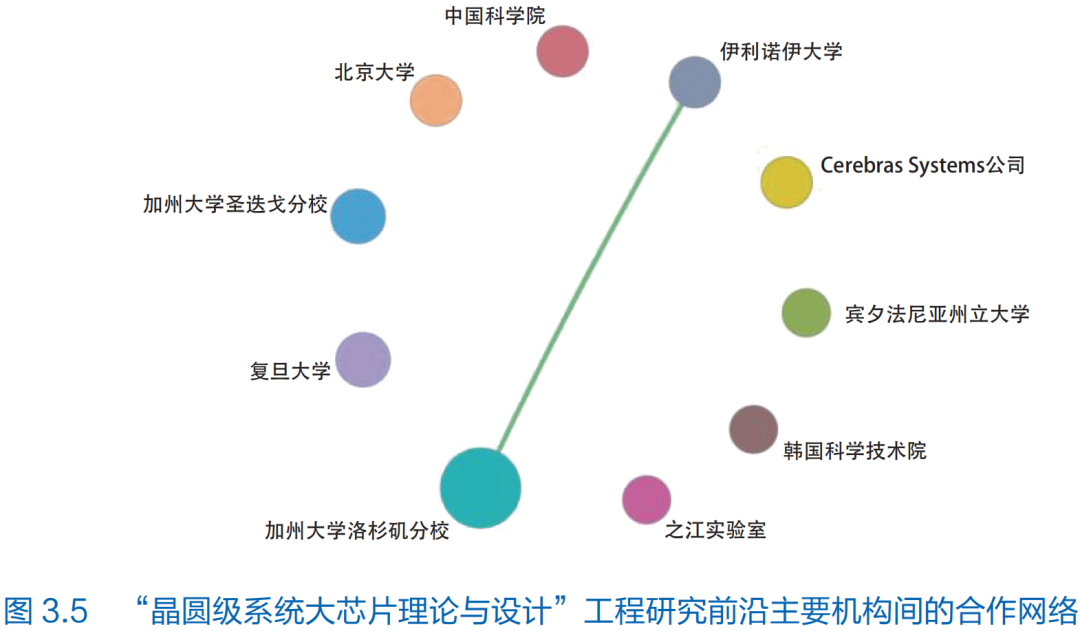

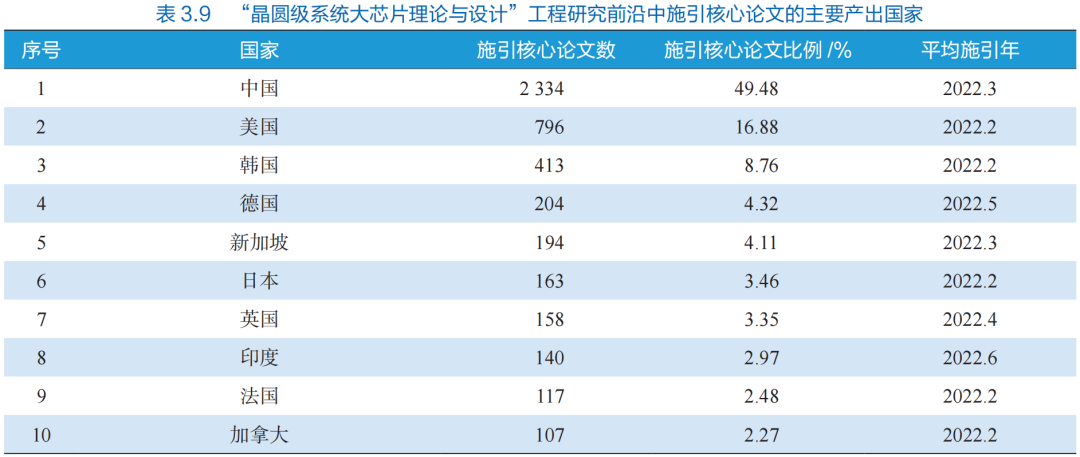

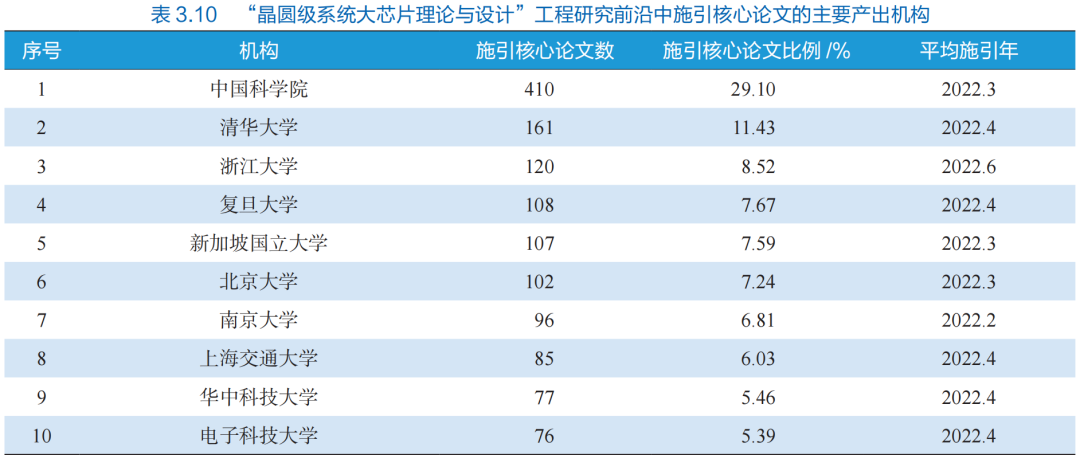

“晶圆级系统大芯片理论与设计”工程研究前沿中核心论文的主要产出国家见表3.7。美国的核心论文数排名第一,占比约为45%,论文平均出版年较早;中国仅次于美国,论文占比约为29%,处于快速追赶状态,平均出版时间较美国晚一年左右。中国与多个国家保持合作,欧洲的德国、英国、瑞士之间相互合作较为密切(图3.4)。在排名前十的核心论文产出机构中,5家来自美国,4家来自中国,1家来自韩国(表3.8)。在机构合作方面,除美国两家机构有合作关系外,其他机构之间鲜少合作(图3.5)。在施引核心论文方面,中国遥遥领先,施引核心论文数接近总数的一半,第二名是美国,其余国家的占比均低于10%(表3.9);在排名前十的施引核心论文产出机构中,除排名第五的新加坡国立大学外,其余均来自中国,体现了中国科研机构对该前沿的高度关注(表3.10)。

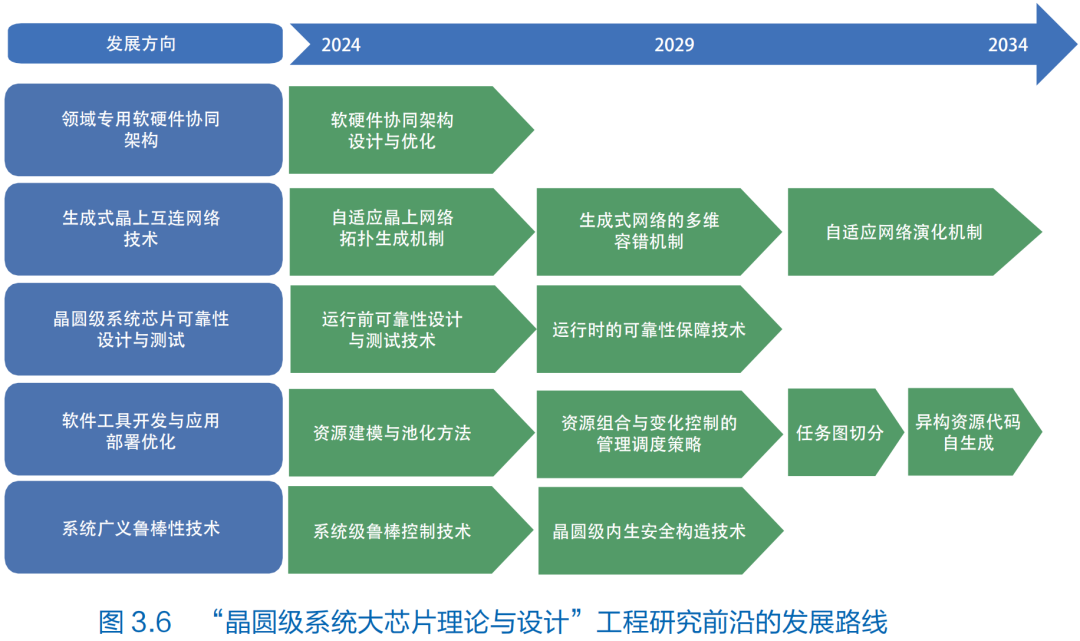

在过去5年中,晶圆级系统大芯片理论与设计取得了诸多研究成果。然而,从整个领域的发展进程看,其应用与研究仍处于起步阶段,存在众多亟待解决的瓶颈问题。该领域未来5~10年的重点发展方向(图3.6)如下:

1)领域专用软硬件协同架构。晶圆级系统大芯片具有计算/存储资源大规模、高密度集成,以及异构资源间低时延、大带宽传输能力等显著特征与优势,能够为适配不同应用的计算架构构建提供广阔的探索空间,但也给领域专用软硬件协同架构的设计和优化带来巨大挑战。

2)生成式晶上互连网络技术。高密度、强可塑的晶上互连网络对晶圆级系统芯片的功能、性能和效能至关重要。生成式晶上互连网络不仅要实现远超现有连接网络的高密度、大规模,还要实现高灵活和强可塑。因此,未来必须开展自适应晶上网络拓扑生成机制、生成式网络的多维容错机制、自适应网络演化机制等关键技术研究,以实现应用服务可软件定义,支撑晶圆级系统芯片的自演化。

3)晶圆级系统芯片可靠性设计与测试。由于高密度的集成架构和高动态的应用结构,晶圆级系统芯片在运行前的可靠性设计与测试及运行时的可靠性保障至关重要。未来研究方向包括晶圆级基板可靠性设计技术、跨尺度高精度高可靠集成技术、晶圆级高可靠供电散热技术、晶圆级可靠性测试与自调节技术等。

4)软件工具开发与应用部署优化。晶圆级系统大芯片大规模、高密度集成资源的多样化组合与应用任务的适配是NP难问题。为充分发挥晶圆级大芯片的优势,实现应用任务在晶圆级大芯片上的部署优化,未来研究重点包括:①晶圆级系统大芯片大规模、高密度集成资源建模与池化方法;②晶圆级系统大芯片支持资源组合和变化的管理调度策略;③充分利用晶圆级系统大芯片带宽优势实现任务图合理切分方法;④面向晶圆级系统大芯片异构资源的代码自动生成方法。

5)系统广义鲁棒性技术。随着面向不同领域应用晶圆级系统芯片的不断增多,不确定物理失效导致的系统鲁棒性问题、继承自异质异构芯粒的安全问题以及由分离制造导致的安全问题将更加严重,晶圆级系统芯片的广义鲁棒性控制技术也必然会引起更多关注。未来研究方向包括如何基于不可信芯粒从系统级构建安全架构并保持系统高性能。晶圆级系统安全芯片架构和硬件防御技术将成为研究重点,包括如何构建内生安全构造结构、如何在安全属性下进行软硬件协同优化等。

内容取自《全球工程前沿2024》

李沛杰,男,1990年出生,博士,山西襄汾人,信息工程大学助理研究员,主要研究方向为软件定义晶上系统、硬件安全、软件定义互连。