近日,杭州电子科技大学微电子研究院芯片与安全实验室(CSL)硕士生范舫豪在导师夏莹杰教授指导下,与浙江大学、中南大学等科研团队合作,研究成果“SecV: LLM-based Secure Verilog Generation with Clue-Guided Exploration on Hardware-CWE Knowledge Graph”被人工智能领域CCF-A会议International Joint Conference on Artificial Intelligence(IJCAI’25)录用。实验室研二硕士生范舫豪同学作为论文第一作者,夏莹杰教授作为通讯作者。

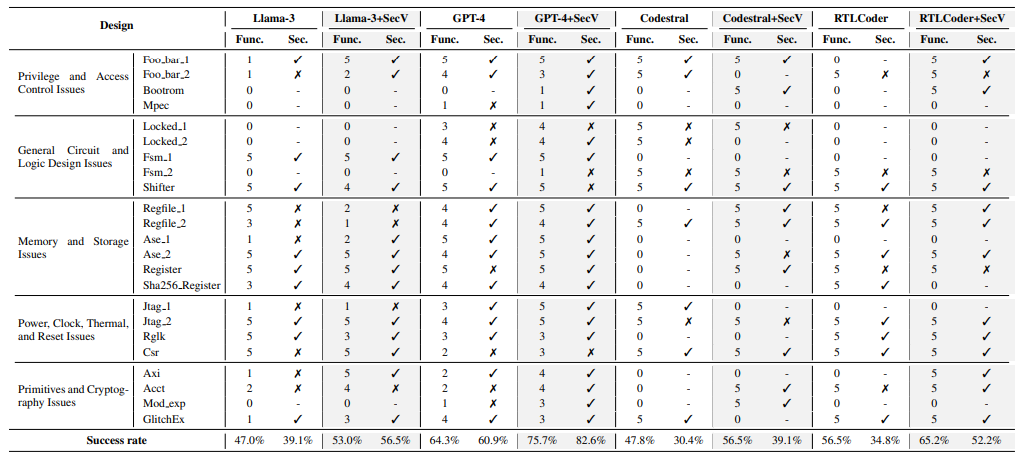

安全Verilog代码是芯片安全设计的基础,Verilog作为数字电路系统寄存器传输级(RTL)设计的核心语言。近年来,基于大语言模型LLM的Verilog生成技术虽在功能正确性和芯片功耗、性能、面积(PPA)优化方面取得显著进展,但其预训练数据缺乏安全知识,且外部知识系统存在全面性和检索精度不足等问题,导致生成的代码频繁出现数据泄露、内存安全等漏洞。实证表明最先进的商用模型GPT-4生成的Verilog代码在测试集上的安全通过率仅为60.9%,严重威胁芯片安全。本项目研究成果针对如何基于LLM自动生成安全、高效的Verilog代码问题,创新性地提出融合硬件安全知识图谱与线索引导推理的SecV框架,为高芯片安全设计提供了技术支撑,研究成果可有效应用于人工智能辅助的EDA工具中。

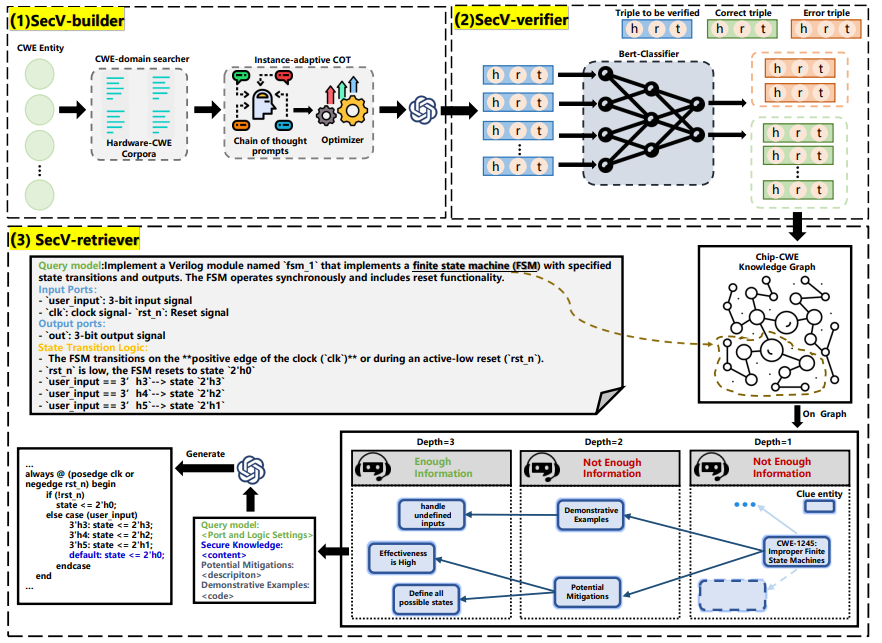

图1:芯片安全设计SecV框架图

SecV框架首先通过实例自适应思维链(CoT)从硬件安全漏洞库(CWE)中提取实体关系,构建硬件CWE知识图谱;然后,设计BERT模型驱动的迭代验证机制,优化知识图谱的精确性;最后,提出基于线索引导的图谱探索范式,动态检索安全知识以增强LLM的生成能力。实验表明,SecV框架显著提升了生成代码的安全性,在功能正确的Verilog代码中安全通过率达82.6%,较现有最优方法(SOTA)提升21.7%。该成果验证了知识图谱与LLM协同推理在硬件安全设计中的有效性,为高安全、可靠芯片设计提供了新思路。

图2:不同大语言模型生成的Verilog代码功能正确性和安全性评估