多年以来,EDA行业一直遵循着固定模式:工程师主导芯片设计决策,工具仅充当运算与仿真的配角。如今,这一传统格局正在被彻底改写。当AI Agent能够主动解析RTL、网表与时序报告,自主开展功耗、性能、面积的多维度折中探索,自治完成约束收敛,乃至主导设计方案的优化迭代,EDA已不再是单纯被动响应的辅助工具,而是进化为拥有主动决策能力的智能体。

当下,包括EDA在内的全球半导体龙头企业,纷纷在智能体AI这一全新赛道全力布局。过去的一个月,Cadence全球首发了面向前端验证的智能体ChipStack;Synopsys宣布正推进多智能体芯片设计与验证工作流;NVIDIA宣布了专为智能体设计的开源大模型……一系列技术突破标志着智能体AI开始全面进入芯片设计领域。

令人振奋的是,国内EDA行业在智能体AI领域也实现重大突破。今天,合见工软发布国内首款智能体AI自研EDA平台——智能体UniVista Design Agent (UDA) 2.0。凭借多项核心能力和行业领先优势,在下一代EDA前沿技术的全球竞争格局中,为国产EDA抢占了战略制高点。

此次升级后,UDA平台正式从智能辅助工具进化为真正意义上的Agentic AI智能体。UDA 2.0是国内首款基于全部自主研发EDA架构上的领先智能体EDA工具,它能够在接受工程人员设计需求和指导后自主完成RTL设计、验证、纠错与优化全流程任务,标志着国产EDA自主式智能体的时代全面开启。合见工软始终致力于大幅提升数字芯片设计效率,为中国集成电路产业应对高复杂度与快速迭代挑战提供核心生产力引擎。

从“辅助工具”到“自主设计者”:AI智能体正在重写EDA的行业规则

随着人工智能的深度发展,Agentic AI(自主式人工智能体)已为芯片设计领域带来范式革命,与传统的“AI + EDA”不同,智能体EDA不再依赖单点模型提供辅助,而是进化为一个具备自主设计能力的决策中枢——它集成了主动规划、独立执行和自我反馈与迭代机制,实现了从辅助分析到主导设计的范式转移。EDA Agent打破了传统的“以人设计为主导,EDA工具辅助”的方法,将工程师从繁琐的实现细节中解放,使其更专注于架构创新、战略规划和复杂决策等更高维度的工作。EDA技术的下一代竞争,将取决于以人工智能为核心的技术突破。

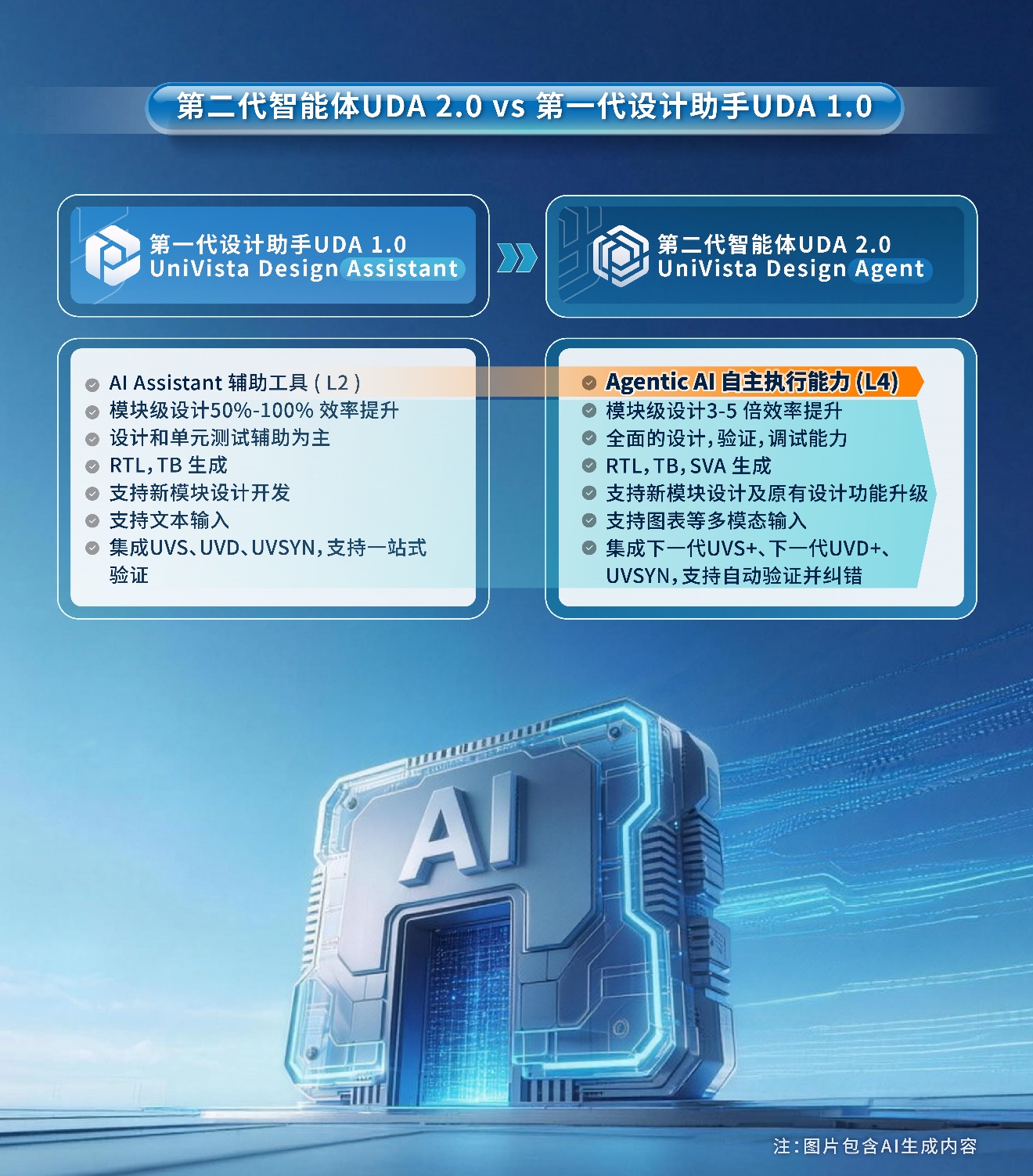

合见工软早在2025年2月就推出了第一代数字设计AI智能平台UDA 1.0,此款产品是国内首款自主研发、专为RTL Verilog设计打造的AI智能平台,提供了全面的AI辅助功能,并已在国内头部IC企业和学术研究机构部署落地。此次UDA 2.0版本的发布,标志着合见的AI赋能产品功能和技术水平的一次飞跃,也代表国产数字EDA在智能化领域的功能覆盖和性能水平正在与国际领先技术齐头并进。

从系统级需求到设计验证的更高层级自动化,工程师则聚焦于创造本身

随着智能体AI深度融入IC设计体系,合见工软的智能体UDA 2.0,已经从“Level 2:对话式 LLM 辅助工具”,演进到“Level 4:Agent 工作流 - 自主设计者”。UDA 2.0与上一代产品相比,其颠覆性突破在于构建了一个具备自主任务规划和执行、自动调用内嵌和外挂工具集完成闭环设计、验证与优化能力的Agentic AI系统。这一系统深度融合了大模型(LLM)与合见工软自研的EDA工具链(包含UVS+软件仿真、UVD+软件调试、UVSYN逻辑综合等),并将芯片设计行业知识深度融入Agentic AI系统中,实现了芯片设计从自然语言描述到高质量代码产出的一站式自动化。其核心价值并不在于单点效率优化,而在于通过智能体理解和规划任务,并通过设计、验证、调试、文档处理等多个智能体协同,直接调用底层EDA工具,通过迭代自主完成整个工作流程并自主修正和优化设计,将工程师从大量重复性工作中解放出来,使其能够更多聚焦于架构决策和创新性设计,从而使芯片的整体项目设计和验证效率实现指数级提升。

智能体UDA 2.0的核心能力和优势包括:

· 代码设计与优化:基于自然语言指令自动生成高质量Verilog RTL代码,支持在现有设计上新增功能开发;支持设计空间探索,让工程师在早期即可快速权衡PPA(Power、Performance、Area,功耗、性能、面积);支持基于合见自研的快速逻辑综合引擎UVSYN的语法纠错、时序面积评估与优化;并可基于设计规范检查并修正代码。

· 验证与调试:内置合见工软自研的UniVista Simulator (UVS+) 仿真引擎和UniVista Debugger (UVD+) 调试引擎,可一站式完成从TestBench、SVA断言生成到仿真验证的全过程;UDA可自主调用仿真和调试工具,基于仿真和调试结果进行代码纠错,并支持UVM框架及智能优化激励以提升测试覆盖率。

· 灵活的交互和部署方式:支持“自主模式”完成从RTL生成到语法规则编译纠错,到设计功能分析纠错,到设计性能分析优化的完整推理链和长程迭代任务流;同时提供代码编辑区交互、模型交互区文件上传和工具脚本调用等多种灵活交互方式。UDA既能成为独当一面的智能代理,也可承担人机协作的角色。UDA支持LLM的内网及云端灵活部署方式,并可支持用户自研LLM。

· 项目与知识管理:具备完整的工程项目管理、多任务并发能力,通过代码库和文档库RAG技术,将历史项目与设计规范转化为可复用的智慧资产,并支持知识问答,实现信息快速获取。

· 全栈国产化及信息安全:全面支持DeepSeek等国产大模型,采用全栈自研EDA工具链,可适配国产GPU,满足全栈软硬件国产化需求。UDA具备完善的后台用户管理、权限管理与会话管理等功能,并支持功能使用统计分析。

清华大学集成电路学院集成电路设计研究所所长张春表示:“清华大学集成电路学院在芯片设计的教学和科研工作中,一直致力于探索如何将前沿技术转化为高效的教学工具和创新引擎。在2025年的《数字集成系统设计》课程中,我们就引入了合见工软的UDA 1.0 平台,将其作为AI赋能芯片设计的教学工具,让学生亲身实践从自然语言需求到高质量RTL代码的实现过程,直观地感受到了AI如何重塑设计流程。

本次升级的智能体UDA 2.0,采用业内前沿的Agentic AI 架构,标志着从‘工具辅助’到‘智能体自治’的范式跃迁,这与我们培养下一代IC工程师的理念深度契合。在教学层面,UDA 2.0 不仅仅是一个编码助手,而是化身为一个具备主动规划与闭环执行能力的‘AI助教’和‘虚拟队友’。用户只需用自然语言提出功能需求与设计约束,UDA便能理解和规划任务,并自主调用EDA工具,完成‘生成-验证-纠错-优化’的完整闭环。在科研工作中,UDA 同样展现出巨大价值,使我们能以前所未有的速度进行设计空间探索,快速验证新的想法,是培养卓越工程师和推动‘AI for Science’的理想伙伴。”

合见工软首席技术官贺培鑫博士表示:“智能体UDA 2.0的核心,是推动数字芯片设计从‘智能辅助’迈向‘智能体自治’。工程师给出需求、约束与规范,UDA 2.0 即可自主完成任务理解与规划,并通过多智能体协同自动编排与调用 UVS+ 仿真、UVD+ 调试、UVSYN 逻辑综合等工具链,形成‘生成—验证—纠错—优化’的闭环迭代,产出可交付的 RTL 与验证资产。依托全栈国产化、内网可部署且安全可控的工程体系,UDA 2.0将工程团队从大量重复性的实现与调试细节中解放出来,让创新真正回到架构决策、系统权衡与关键工程判断上。”

合见工软此次推出的第二代数字设计AI智能平台——智能体UDA 2.0,打造了创新的芯片设计范式,它标志着合见自主自研的国产AI EDA产品从点状的AI辅助功能,迈入了流程级的AI自主驱动新阶段。智能体UDA 2.0的发布,是合见工软在“EDA+AI”战略上的关键里程碑。作为国产数字EDA与IP领域的先行者和领跑者,合见工软深度布局数字芯片全流程EDA工具、高速接口IP及智算组网IP等关键赛道,已获得国内诸多IC企业的广泛认可与规模化部署,核心产品市场占有率稳居行业前列。

凭借扎实的技术积淀与产品实力,合见工软正为中国半导体产业破解数字大芯片设计的“卡脖子”难题提供坚实支撑。面向未来,公司持续深耕“EDA+AI”前沿方向,以前瞻性创新推动芯片设计范式向更智能、更高效、更安全演进,致力于为中国集成电路产业攀登世界高峰筑牢强有力的技术基座。

据悉,UDA 2.0现已提供商用版本。欲了解更多详情,申请试用或购买相关产品,欢迎垂询sales@univista-isg.com。