2月16日-20日,第72届国际固态电路会议(IEEE International Solid-State Circuits Conference, ISSCC)在美国旧金山召开,集成电路科学与工程学院模拟与混合信号电路研究组在该会议上发表2篇学术论文。研究内容涉及模数转换器(ADC)和时钟参考源芯片。

论文一:A Fully Dynamic Noise-Shaping SAR ADC Achieving 120dB SNDR and 189dB FoMs in 1kHz BW.

该工作发表于2025年ISSCC会议的Noise-shaping and SAR-based ADCs分会场。集成电路学院2023级硕士生赵晗和2022级直博生张煊昊为论文共同第一作者,通讯作者为刘佳欣特聘研究员,电子科技大学为论文第一单位。

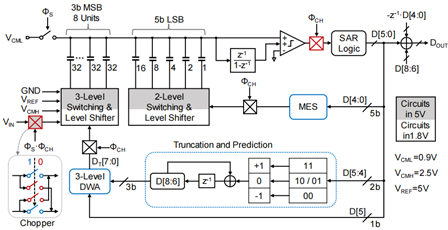

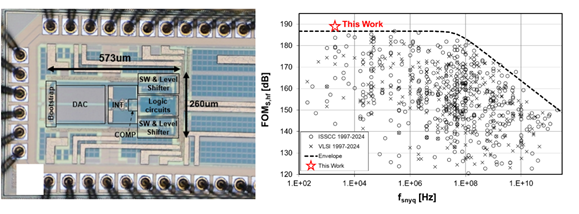

微瓦级功耗和千赫兹量级带宽的高分辨率ADC在便携式仪器、植入式设备和智能传感器中有着广泛的应用。面对此类需求,研究团队提出了一系列创新措施,研制出一款全动态工作的低功耗高精度噪声整形ADC芯片。该芯片采用动态原件匹配和误差反馈混合的失配误差整形方法,高效解决了DAC失配的问题;采用基于三电平开关策略的动态原件匹配技术,在解决电容失配的同时,将功耗降低了一半;采用基于悬浮放大器的积分器实现了全动态操作,消除了静态功耗;采用全局斩波技术抑制低频噪声并进一步改善线性度。该ADC芯片实测达到了120.6dB的信噪失真比(SNDR)和132dB的无杂散动态范围(SFDR),这两项指标均为目前学术界报道的最高水平;芯片整体功耗仅139.1μW,且功耗随采样率可等比缩放,Schreier FoM为189dB,达到了现有ADC芯片中最高的能效优值。

图1 ADC系统架构图

图2 ADC芯片照片及其在ADC性能统计图中的位置

论文二:A 0.4μW/MHz Reference-Replication-Based RC Oscillator with Path-Delay and Comparator-Offset Cancellation Achieving 9.83ppm/℃ from -40 to 125℃

该工作发表于2025年ISSCC会议的Analog Techniques分会场。集成电路学院2022级博士生刘悦多为论文第一作者,通讯作者为杨世恒研究员,电子科技大学为论文第一单位。

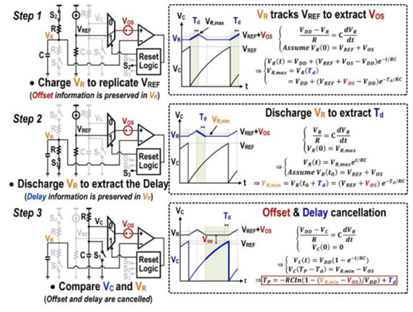

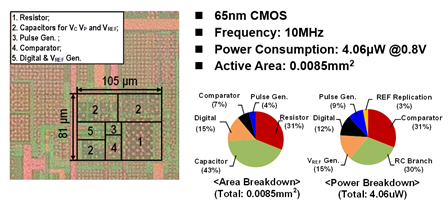

该工作研制出一款高精度高鲁棒性RC时钟参考源芯片。创新性地提出了一种基于参考源复制技术的比较器失调与路径延时消除方案,解决了传统开环RC振荡器温度与电压稳定性较差的问题;集成动态功耗调节技术,提升了整体能量效率。该芯片采用65nm CMOS工艺,在0.8V的供电电压下实现了高温度稳定性(9.83 ppm/℃),超低功耗(0.4 µW/MHz)和小面积(0.0085 mm2)。同时达到了目前RC振荡器芯片最高的174dB温度-功耗FoM和285dB功耗-抖动FoM。这一技术为物联网,电子通讯等领域的时钟芯片提供了新的解决方案。

图3 本研究提出RC振荡器的工作流程

图4 本研究的芯片图与面积功耗占比

国际固态电路大会(ISSCC)是国际集成电路领域的顶级会议,每年2月中旬在美国旧金山召开,是国际公认的规模最大、最权威的芯片设计领域学术会议,有着“芯片奥林匹克(Chip Olympic)”的美誉。历史上入选ISSCC的论文都代表着当前全球顶尖水平,展现出芯片技术和产业的发展趋势,许多集成电路领域里程碑式的发明与技术突破均在该会议首次发布。

评论

文明上网理性发言,请遵守新闻评论服务协议

登录参与评论

0/1000