1.221家半导体公司Q1业绩排行榜:超6成公司净利同比增长 46家实现翻倍

2.苹芯科技 N300 存算一体 NPU,开启端侧 AI 新征程

3.半导体工艺 “军备竞赛”将转向 High-NA EUV,2nm 只是起点

4.Chiplet的崛起之路,如何突破困局?

5.美国芯片关税征收倒计时,税率高达100%?半导体厂商屏息以待

6.三星代工业务再遭打击,AMD放弃采用其4nm制程技术

7.美议员拟推新法案:追踪英伟达AI芯片去向,遏制对华偷运

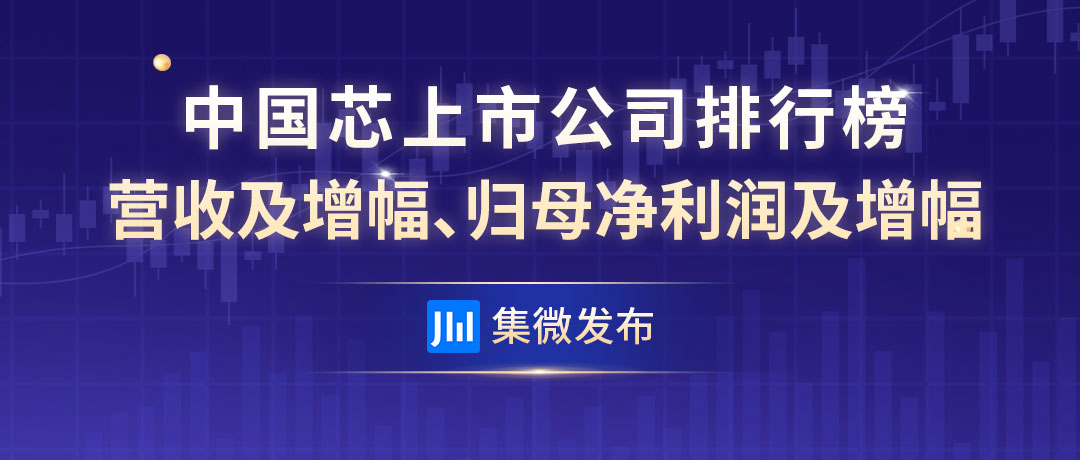

1.221家半导体公司Q1业绩排行榜:超6成公司净利同比增长 46家实现翻倍

截至4月底,A股上市公司一季报披露已接近尾声。经过梳理,笔者发现,在人工智能、国产替代等热点的有力推动下,多家半导体公司一季度业绩表现不俗,纷纷交出了一份亮眼的成绩单。

据集微网不完全统计,截至4月30日,A股有221家半导体公司披露了2025年一季度度报告,超过7成公司营收出现同比增长;盈利方面,更是有134家公司归母净利润出现同比增长,占比高达60.63%,超过六成。

221家企业合计营收2233亿元

据集微网统计的A股半导体公司2025年一季度业绩显示,221家公司实现营业收入合计2233.07亿元,平均每家企业10.1亿元。

从业绩规模来看,营收超过100亿元的公司有4家,分别是中电港、环旭电子、楚江新材、闻泰科技,其营收分别为174.7亿元、136.49亿元、131.46亿元、130.99亿元。

营收在50~100亿元(含)区间的企业有6家,长电科技、北方华创、太极实业、韦尔股份、通富微电、纳思达,其营收分别为93.35亿元、82.06亿元、67.19亿元、64.72亿元、60.92亿元、59.27亿元。

营收在30~50亿元(含)区间的企业有6家,三安光电、江波龙、华天科技、深科技、晶盛机电、士兰微,其营收分别为43.12亿元、42.56亿元、35.69亿元、33.65亿元、31.38亿元、30亿元。

营收在15~30亿元(含)区间的企业有21家,分别是晶合集成、海光信息、华润微、中微公司、雅克科技、兆易创新、有研新材、三环集团、好上好、思特威、芯联集成、扬杰科技、佰维存储、晶晨股份、格科微。

营收增幅方面,有172家公司营收实现同比增长,占比达到77.83%。其中,营收增幅超过50%区间的企业有32家,占比14.48%;营收增幅在20%~50%(含)区间的企业有58家,占比达到26.24%;营收增幅在0%~20%(含)区间的企业有84家,占比达到38%;营收增速同比下降的企业有49家,占比为22.17%。

从增长幅度来看,寒武纪的营收同比增长幅度最高,达到4230.22%,紧随其后则是ST铖昌、芯动联科,其2025年一季度营收分别同比增长365.26%、291.77%。

营收增幅在100%~200%之间的企业有6家,分别是云天励飞、仕佳光子、和林微纳、思瑞浦、思特威、锴威特,其营收同比增幅分别为168.23%、120.57%、115.95%、110.88%、108.94%、100.91%。

营收增幅在50%~100%之间的企业有23家,分别是智立方、纳芯微、万业企业、神工股份、长光华芯、澜起科技、精测电子、康希通信、东微半导、瑞芯微、炬芯科技、杰华特、德邦科技、伟测科技、京仪装备、艾森股份、灿勤科技、敏芯股份、恒玄科技、广立微、全志科技、海光信息,以及拓荆科技。

营收同比增幅在40%~50%(含)区间的企业有14家,分别是中电港、芯朋微、峰岹科技、路维光电、上海新阳、长川科技、希荻微、华峰测控、安集科技、乐鑫科技、赛微微电、泰凌微、盛美上海,以及源杰科技。

营收同比增幅在30%~40%(含)区间的企业有19家,分别是晶华微、凌云光、北方华创、长电科技、黄山谷捷、汇成真空、中微公司、思科瑞、臻镭科技、捷捷微电、华海清科、东芯股份、日联科技、美芯晟、国民技术、联特科技、雅克科技、慧智微、甬矽电子。

34家公司归母净利润翻倍增长

2025年一季度,有163家A股半导体公司归母净利润实现盈利,合计盈利152.52亿元,另有58家企业净利润出现亏损,共计亏损32.44亿元。

从归母净利润规模来看,221家企业中,共有6家企业净利润超过5亿元,占比达到2.71%;净利润在1~5亿元(含)的企业有36家,占比为16.29%;净利润在0~1亿元(含)的企业有121家,占比54.75%;净利润亏损的企业有58家,占比为26.24%。

具体来看,归母净利润超过5亿元的公司有6家,分别为北方华创、韦尔股份、晶盛机电、三环集团、澜起科技、海光信息,其归母净利润分别为15.81亿元、8.66亿元、5.73亿元、5.33亿元、5.25亿元、5.06亿元。

归母净利润在2-5亿元之间的企业有13家,分别为寒武纪、环旭电子、中微公司、扬杰科技、闻泰科技、雅克科技、盛美上海、兆易创新、华海清科、顺络电子、三安光电、瑞芯微、长电科技,其归母净利润分别为3.55亿元、3.35亿元、3.13亿元、2.73亿元、2.61亿元、2.6亿元、2.46亿元、2.35亿元、2.33亿元、2.33亿元、2.12亿元、2.09亿元、2.03亿元。

归母净利润在1-2亿元之间的企业有23家,分别是汇顶科技、思特威、恒玄科技、晶晨股份、深科技、安集科技、江丰电子、士兰微、睿创微纳、鼎龙股份、复旦微电、晶合集成、楚江新材、中瓷电子、飞凯材料、紫光国微、太极实业、捷捷微电、长川科技、新洁能、火炬电子、斯达半导、通富微电。

在归母净利润增幅方面,134家企业净利润出现同比增长,占比达到60.63%。其中,净利增幅超过100%的企业46家,占比为20.81%;净利增幅在50~100%(含)的企业23家,占比为10.41%;净利增幅在0~50%(含)的企业65家,占比为29.41%;另外,净利增长率下降的企业有87家,占比39.37%。

从净利润增长幅度来看,有研新材归母净利润同比增长14698.12%,居于首位。紧随其后分别是伟测科技、芯动联科、长川科技、神工股份、思特威、博通集成、士兰微、仕佳光子,增幅分别为8577.53%、2869.17%、2623.82%、1850.7%、1264.97%、1256.1%、1072.43%、1003.79%,均超过1000%。

归母净利润增幅在300%-1000%(含)之间的企业有13家,分别是泰凌微、恒玄科技、和林微纳、晶瑞电材、联特科技、臻镭科技、智立方、英集芯、苏州固锝、炬芯科技、精测电子、凌云光、*ST铖昌,其归母净利润增幅分别为910.55%、590.22%、589.99%、582.15%、499.92%、495.74%、488.96%、395.62%、395.6%、385.67%、336.06%、324.49%、300.06%。

归母净利润增幅在100%-300%(含)之间的企业有24家,分别是盛景微、好上好、寒武纪、

ST华微、瑞芯微、盛美上海、台基股份、上海新阳、甬矽电子、华峰测控、江丰电子、宏微科技、东田微、华润微、澜起科技、思瑞浦、美芯晟、赛微电子、敏芯股份、赛微微电、慧智微、概伦电子、侨源股份,以及飞凯材料。

从整体表现来看,2025年一季度,A股半导体公司的经营业绩十分亮眼,展现出强劲的增长势头。

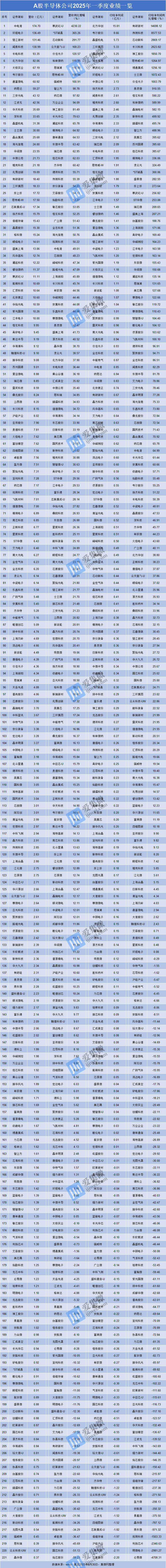

2.苹芯科技 N300 存算一体 NPU,开启端侧 AI 新征程

随着端侧人工智能技术的爆发式增长,智能设备对本地算力与能效的需求日益提高。而传统冯·诺依曼架构在数据处理效率上存在瓶颈,“内存墙”问题成为制约端侧AI性能突破的关键掣肘。在这一背景下,存算一体芯片凭借低功耗、高带宽,以及相对的通用性能,正在成为赋能智能终端、物联网设备以及边缘计算场景的核心动力。

科技创新企业苹芯科技深耕存算一体技术,推出N300存算一体NPU,在不改变传统MCU形态的同时为传统MCU芯片赋予AI能力,突破传统MCU的算力瓶颈,为端侧设备加载AI提供了革命性的解决方案。苹芯科技在接受集微网采访时表示,目前存算一体技术在国内外企业的不懈努力下已经实现商业化应用,存算一体芯片也即将全面进入千行百业,为人工智能的大规模应用提供不竭的算力支撑。

架构创新,存算技术释放数十倍能效比提升

存算一体并非最新提出的概念,发展历程可以追溯到上个世纪。1969年,斯坦福研究所的Kautz等人首次提出了存算一体计算机的概念,旨在将计算单元与存储单元融合,实现数据存储与计算的同步进行。此后,多伦多大学(1992年)和伯克利实验室(1997年)都相继尝试以逻辑电路的形式拉近存储与计算的距离。

2000年以后,随着大数据以及人工智能技术的发展,人们对于并行计算的需求日益增长,存算一体技术受到更多关注。特别是Transformer架构的流行,生成式模型已经出现上千亿,甚至更高参数量的需求,对存储的要求也越来越高、带宽越来越大。传统冯·诺依曼架构的数据搬运模式很难满足AI芯片的计算效率,这就给存算技术带来了新的商业化空间。

根据苹芯介绍,传统芯片是先把数据从存储系统中读取出来,放到计算单元当中进行运算,然后再把计算结果传回到存储系统当中。这种大规模的数据迁移导致了带宽的瓶颈和功耗的浪费。存算一体的核心创新在于“计算发生在数据存储的位置”。它从根本上避免了上述情况的发生,同时带来一系列的性能优势。以苹芯科技开发的SRAM存算单元为例,它直接在存储器内部完成乘累加运算,彻底消除了数据搬运需求。测试数据显示,这一技术可将数据迁移能耗降低90%以上,同时将能效比提升至27.38 TOPS/W,较传统架构提升数十倍(该成果已入选ISSCC 2022)。

目前,存算一体技术的商业化进程已处于成熟落地应用阶段,大规模应用即将全面铺开。比如搭载了存算一体NPU的MCU芯片,已用于智能监控摄像头等设备中,实现人脸识别、行为分析、目标检测等视频图像的实时分析和处理;在智能手表、智能手环等设备中,进行心率监测、运动姿态识别等时实数据监测和分析。

聚焦终端侧,规模商业化突破的现实选择

通常,工业界在评价一个架构的商业化前景时,除了关注技术层面的发展潜力以外,还要考虑通用性、快速迭代能力,以及成本等核心指标。此外,相比冯·诺依曼架构来说,存算一体架构的专用性更强。由于从设计上是将计算单元与存储单元融合在一起,在进行技术迭代时也会面临更多的挑战。这些都是业界探索存算一体技术应用落地时,需要考虑的要点。因此,苹芯指出,相对于云端高度复杂的生态、技术挑战,率先从终端侧寻求突破是更加现实的选择。

首先,云端计算往往被定位成一个平台,因而更加强调泛化能力,也就是计算的通用性。这对更倾向于专用计算的存算一体芯片来说,设计上更具挑战性。但是在终端侧和边缘侧的MCU芯片进行的更多是一项或者几项指定功能,比如人脸检测、语音识别等。这就意味着,终端侧的芯片并不需要那么强的平台化能力,它的应用是相对固定的,因而算法也相对固定,与之相匹配的计算和存储的能力也就相对固定。这就让存算一体芯片有了更多用武之地。

其次,很多终端侧的应用场景对芯片的能效比有着极高的要求,一方面要求产品具有轻量化、便携化的趋势,需要考虑无法插电源工作的情况;另一方面又有着从非AI转向AI类产品的升级需求。这就需要有高能效比的技术来支撑,在这方面存算一体芯片更具优势。

此外,终端侧的市场空间同样足够广阔。机构预测,2025年可穿戴类产品的市场规模将超过1000亿元。今年CES大展上,AI眼镜和AI玩具成为最火爆的两类新品。预计2025年全年AI眼镜出货量可达几百万台,WellsennXR预测到2029年全球AI眼镜销量或将突破5500万副,渗透率将提升至3.48%,市场规模更是有望突破825亿元。人工智能向端侧市场的大规模渗透已经开始。

正是基于这样的判断,苹芯科技面向终端侧模型,推出了基于SRAM的存算一体NPU——N300。这是一款可集成于SoC芯片当中的IP核,可用于执行神经网络的加速任务。NPU可以提升神经网络效率,涵盖矩阵加速、非线性加速等功能。用户基于NPU可以打造端侧SoC、MCU等产品。苹芯表示:“苹芯科技的比较优势在于产品的快速迭代能力,强调以小成本的迭代方式,小步快跑、快速验证,为实现存算一体技术的大规模商业化提供了必要条件。”

此外,N300 在架构设计、性能指标(如算力、功耗、带宽等)方面还有许多创新之处,比如存算融合阵列:256KB SRAM中嵌入计算单元,面积效率达0.26TOPS/mm²;动态精度引擎:支持4-16bit混合精度,语音模型量化后精度损失<3‰;多核弹性扩展:单核0.5TOPS,十六核集群可达8TOPS,工业质检场景吞吐量提升273%。

这些技术指标与性能集于一体,使N300具备了成为终端侧优秀AI解决方案的潜在实力。

生态与模式,N300在实际应用中的优势所在

目前,有越来越多MCU厂商开始将AI功能深度嵌入到芯片设计之中,包括ST、瑞萨、恩智浦以及众多国内企业。它们大多采用集成NPU的方案,让芯片得以在端侧直接执行图像识别、语音识别、预测分析等AI任务,减少对数据回传云端的依赖。

为了满足用户的需求,苹芯科技也在不断调整自身的商业模式。首先,苹芯科技不仅推出N300 存算一体IP核,还同时开发了一款SoC芯片——S300,在神经网络加速部分集成了基于28nm工艺的N300内核,主打多模态和环境感知功能。这一方面使苹芯科技具备了向系统厂商提供芯片级解决方案的能力,也意味着N300 作为一款IP核是已经得到验证的产品,芯片级用户在采用它的时候,无需担心产品的可靠性。

其次,在生态方面,N300 支持开源编译器TFLM。AI加速芯片并不像存储芯片那样是一个标准化的产品,可能100家NPU公司,就有100种解决方案。不过目前很多MCU公司已经支持开源框架。而N300支持TFLM,意味着与多数MCU公司采用了同一框架,这样在软件上就与MCU是统一的。芯片用户可以直接使用N300方案进行训练,实现一键部署。

第三,N300是一款多模态融合感知NPU,对于语音、图像,以及其他传感数据都能给予支持。也就是说,在终端侧的有限应用中,它是可以做到相对通用,与其他面向终端侧专用解决方案相比,具有更强的泛化优势,确保了客户的易用性。

再加上存算一体芯片天然具有的能效比优势、带宽优势,N300完全具备成为一款面向终端侧AI市场优秀解决方案的产品素质。事实上,N300已经在市场小范围推广,并取得不少成功的商业化案例。

以TWS耳机降噪案例为例,近年来TWS耳机市场火热,很多厂商采用AI方案实现本地化语音增强与环境降噪。N300可被集成在22nm工艺的芯片当中,实现36 GOPS@64MHz的算力,支持DCCRN网络(含LSTM)的实时推理。适配了微型化的终端设计;同时发挥极强的功耗控制效能,平均工作功耗<1mW,比传统的DSP方案降低70%,延长耳机续航30%以上。

继续深耕,苹芯科技为边缘未来布局

展望终端与边缘侧AI市场发展趋势,“存算一体”技术完全有能力成为该领域的主流芯片架构之一。苹芯表示,未来的计算架构大致有三条发展路径:一是存算一体。其将计算单元与存储单元融合,在实现数据存储的同时直接进行计算,以消除数据搬移带来的开销。二是3D堆叠。这种架构出于对存储带宽的极致追求,因此是天然是反对存算一体的。第三条路径则是在前两种方案之间做平衡,也即近存计算。它希望在不改变计算单元,也不改变存储单元的情况下,尽量缩短存储与处理器中间的距离,以此改善芯片的性能。

在这三条路径中,如果计算和存储功能相对明确,那么存算一体方案就更具优势,可以更加充分发挥架构带来的优势。当然,目前的存算一体要想实现大规模商用仍有很多技术瓶颈需要突破,包括工艺兼容性的改善,比如eNVM存储器的稳定量产;提高设计工具链的成熟度,实现自动化EDA工具与跨平台编译器的支持,加强代工厂标准IP库的建设与优化多场景下的制造成本,以便提高产业链的整体协同能力。同时还需要构建开源生态,以解决开发门槛高、改善算法适配碎片化等问题。这样才能将存算一体从技术优势转化为规模化落地的能力。而苹芯科技的优势在于能够在较短时间内,只要客户立项并确定其所采用的工艺,就可以进行快速定制并实现交付。这可以成为用户大规模商用中的一大助力。

从市场角度来看,未来3~5年,存算一体芯片将在AIoT和边缘计算领域迎来爆发式增长,市场潜力集中于实时健康监测(如可穿戴ECG实时分析)、工业预测性维护(振动/温度信号边缘诊断)及智慧家居(能效优化、数据安全与保护)等场景,这就需要高能效比与低成本的产品,精准匹配边缘侧对“高能效+低成本+实时处理”的核心需求。

苹芯科技已经推出支持图像、语音等多模态融合处理的N300 ,未来将把这些核心能力,比如CNN/Transformer硬件加速、动态数据流调度引擎向更多模态扩展,推出新的解决方案。“存算一体仍然处于快速发展阶段,这个技术是不断被唤醒的,不断有新的热点出现。我们已经推出一颗芯片和一个IP,实现了多模态融合感知。下一步我们将开发一款LPU(语言处理单元)方向的产品,针对CNN/Transformer硬件加速,把传送这件事情做到边缘侧去。”苹芯透露。

为此,苹芯科技未来将聚焦22/14nm工艺升级与新型eNVM(如MRAM/RRAM)存算架构集成,通过混合精度计算优化和稀疏化加速引擎提升算法效率,同时完善开源编译器工具链(支持多模态模型一键部署)并拓展异构计算IP库。

苹芯科技还计划在未来的研发工作中,进一步提高存算一体核心单元计算能效比,并联合代工厂推进eNVM工艺量产,构建覆盖智能穿戴、智慧家居等场景的“存算+”生态,突破设计自动化工具与跨平台适配瓶颈,加速技术规模化落地。

3.半导体工艺 “军备竞赛”将转向 High-NA EUV,2nm 只是起点

随着2nm量产在即,英特尔、三星、台积电以及IMEC等研究机构都将工艺开发的重点瞄准了新一代工艺技术。进入埃米时代,先进工艺的开发与生产大概率将采用High-NA EUV光刻机,对于High-NA EUV及相关工艺的研究也热了起来。ASML与Imec于3月中宣布签署新的战略合作伙伴协议,重点关注半导体研究与可持续创新。 Imec也与蔡司加强合作,目标指向High-NA EUV及相关工艺的应用与开发。

2nm 工艺竞速

2nm的量产与应用是2025年全球半导体产业一大看点。台积电、英特尔、三星都将交付2nm的时间点订在2025年。

台积电在2025年北美技术研讨会上透露,该公司有望在今年下半年开始大规模生产N2(2nm 级)芯片,将实现所谓的“全节点改进”,首个依赖环绕栅极(GAA)纳米片晶体管的生产技术。与N3E相比,性能提升10%至15%,功耗降低25%至30%,晶体管密度提升15%。产能在年底前有望达到5万片,甚至有机会迈上8万片台阶。

英特尔在此前召开的2025愿景大会上也宣布,其Intel 18A工艺节点已进入风险生产。这是一个关键的生产里程碑,标志着该节点目前处于小批量测试生产运行的早期阶段。英特尔处理器Panther Lake很可能是风险生产的产品。有消息称,在未来举行的2025年VLSI研讨会上,英特尔将详细介绍18A的情况。综合此前释出的资料,18A制造技术是英特尔首个采用环绕栅极(GAA)RibbonFET晶体管并采用PowerVia背面供电网络(BSPDN)的节点。与采用Intel 3工艺技术制造的相同模块相比,Intel 18A制造工艺在相同电压(1.1V)和复杂度下,性能提升25%,在相同频率和1.1V电压下,功耗降低36%。

三星电子的晶圆代工部门财务状况不佳,继2023年录得2万亿韩元的运营亏损后,去年该部门的亏损额预计翻倍至4万亿韩元,2025年可能再亏损3万亿韩元。自全永铉(Jeon Young-hyun)接任半导体部门负责人以来,该公司已放缓资本支出。但是,三星电子并没有放缓对先进工艺的开发。有消息称,三星的新一代自研移动处理器Exynos 2600将采用自家2nm工艺(SF2),目前试产初始良率达到了预计的30%。另有消息称,高通的下一代处理器的代工生产也将再度探索使用双重采购方案 ,利用台积电和三星代工厂的技术来降低生产成本。

伴随2nm工艺的推进,厂商也在提前布局再下一代工艺的开发。据报道,三星电子目标在2027年将1.4nm的SF1.4制程量产。在2025年北美技术研讨会上台积电还透露了计划在2026年底推出A16芯片制程,2028年开始使用A14制程的计划。而根据英特尔代工的最新路线图,Intel 14A(1.4nm级)节点将于2026年投入生产,Intel 10A(1nm级)将于2027年底开始开发或生产。在此情况下,各大厂商对High-NA EUV光刻工艺开发也提上议程。

EUV光刻工艺持续进阶

英特尔是首家购买 High-NA EUV光刻机的芯片厂商。2024年,英特尔在其位于俄勒冈州希尔斯伯勒附近的D1开发工厂安装并开始使用两台ASML High-NA Twinscan EXE:5000 EUV。英特尔工程师 Steve Carson在此前召开的2025年SPIE先进光刻 + 图案会议上透露,已使用这些系统在一个季度内处理了多达3万片晶圆。英特尔工厂的早期结果显示,高数值孔径机器仅用一次曝光和“个位数”的处理步骤就能完成早期机器需要三次曝光和大约40个处理步骤才能完成的工作。

imec也在2025年SPIE 先进光刻+图案会议上展示了在单次曝光High-NA EUV光刻后图案化的20nm间距金属线结构上获得的首个电气测试结果,使用金属氧化物(MOR)负性光刻胶进行单次High-NA EUV图案化后获得的 20nm 间距的金属化线结构表现出 90% 以上的良率。此外,imec 还宣布在其与 ASML 合作的High-NA EUV光刻实验室首次成功利用High-NA EUV光刻机曝光了逻辑和 DRAM 的图案结构。在逻辑图案方面,成功图案化了单次曝光随机逻辑机构,实现了9.5nm 密集金属线(对应 19nm Pitch),将端到端间距尺寸降低至 20nm 以下,还实现了中心间距 30nm 的随机通孔,展现了出色的图案保真度和临界尺寸一致性,并构建了 P22nm 间距的二维特征,显示了新一代光刻技术在二维布线方面的潜力。在 DRAM 领域,成功利用单次曝光图案化了集成 SNLP 和位线外围的 DRAM 设计,展现了High-NA EUV减少曝光次数的能力。

三星是业内首批成功将EUV工艺应用于DRAM生产的公司之一,在 EUV 工艺方面占据优势。但三星目前在1a DRAM的量产竞争中落后于 SK 海力士。为了提升竞争力,三星正积极引进High-NA EUV设备,预计 2025 年中期开始运行其首台High-NA EUV光刻机。据悉,SK 海力士也在购买 High-NA EUV设备,预计 2025 年下半年首批接收这些设备。

同时也有消息称,台积电为了满足2nm的量产需求,也加大了对EUV光刻机的采购力度,其在2024年就订购了30台,并且计划在2025年再订购35台,其中包括High-NA EUV光刻机。此前台积电并未把如此高价格的High-NA EUV作为重点。

EUV 光刻机的迭代蓝图

ASML的标准型数值孔径极紫外光刻机(NA EUV)目前可以打印13.5纳米的关键尺寸,通过单次曝光,可以产生26nm的最小金属间距和25-30nm尖端到尖端的近似互连空间间距,这一尺寸可以进行4/5nm节点制程的生产。然而,业界仍在不断推进先进制程的脚步。

如果想要再进一步提升EUV光刻机的分辨率就要从NA指标上下手。“NA”即光学系统的数值孔径,表示光线的入射角度。使用更大的NA透镜可以打印出更小的特征尺寸,标准EUV使用的是NA=0.33的物镜系统,High-NA EUV使用的是NA=0.55的光学系统。分辨率也由13.5nm提升到了8nm,可以实现16nm的最小金属间距,对于2nm以下制程节点非常有用。

Imec预计,即使对于1nm节点,High-NA EUV系统也能提供解决方案。另外,在生产效率方面,High-NA EUV系统每小时可光刻超过185片晶圆,与已在大批量制造中使用的EUV系统相比还有所增加。ASML还制定了到2025年将High-NA EUV的生产效率提高到每小时220片晶圆的路线图。

除High-NA EUV外,有消息表示,ASML还在计划开发更新一代Hyper-NAEUV光刻机。ASML 前总裁兼首席技术官、现任公司顾问 Martin van den Brink 在2024年的 imec ITF World 的演讲中表示,ASML 计划在 2030 年左右正式推出 Hyper - NA EUV 光刻机,其数值孔径(NA)将达到 0.75,以便实现更高分辨率的图案化及更小的晶体管特征。

从目前人们规划的晶体管技术路线图来看,2030年将进入7埃米(0.7nm)时代,2032年有望演进到5埃米(0.5nm),2036年有望实现2埃米(0.2nm)。这就有必要开发再下一代的EUV光刻机。

如果想要进一步推进光刻设备的进步,比如开发Hyper-NA EUV,增加投影光学元件的数值孔径,将面临更多挑战。一方面,光的偏振问题较为突出,从 0.55NA 左右开始光的偏振就会影响对比度,高于 0.55NA 时偏振会破坏对比度,需要偏振器来避免,但偏振器会阻挡光线、降低能效并增加生产成本。标准EUV Twinscan NXE 售价约为1.83 亿美元。High-NA EUV 的Twinscan EXE的售价约为3.8 亿美元。未来的Hyper-NA EUV的成本预计将会更高。另一方面,光刻胶方面也存在挑战,在 0.55NA 时光刻胶就已经变薄,这将给蚀刻选择性带来更多挑战。

不过,目前 Hyper - NA EUV 光刻机还处于早期开发阶段,距离实际量产和应用还有较长时间,相关技术仍在不断研究和探索中。

4.Chiplet的崛起之路,如何突破困局?

半导体行业对Chiplet(芯粒)的优势赞不绝口,包括更快的上市时间、更出色的性能以及更低的功耗,但要在定制化和标准化之间找到恰当的平衡,其难度远超最初的预期。

商用Chiplet市场要真正腾飞,需要对Chiplet的独立运作和整体运作方式有更深入的理解。需要一种一致的方式将Chiplet彼此连接,并将其连接到各种其他组件,对其进行特性描述,以便它们能够在多种设计中重复使用,并对其进行封装和测试。最重要的是,需要一种在设计过程伊始就更轻松地完成所有这些工作的方法。虽然这与软核(Soft IP)市场有一些相似之处,但转向本质上是强化IP集合的市场需要更多的结构和热分析、更多的物理知识,以及对所有组件的封装和最终使用方式有更深入的理解。

“每个Chiplet都是一块独立的硅片,但它也是主系统内部的一个子系统。它很独特,因为它不像SoC里的子系统。”Cadence工程师Moshiko Emmer说道,“它必须在某种程度上保持独立。你需要单独流片。之后你还需要拿回硅片。在将它集成到主系统之前,你至少需要对其进行彻底的测试和调试,这意味着它必须具备一些独立的功能,或者说所有的控制功能,所以这里需要一些复杂的架构。”

如今,多芯片组件的标准很少,大多数是由大型系统和高性能计算(HPC)处理器公司开发的,主要使用内部开发的Chiplet。这种情况预计在未来几年内会有所改变,但这将取决于更标准化的芯片集成方案的普及,这样就无需从头开始开发所有组件了。

“例如,如果你看一下架构标准,就会发现Arm Chiplet系统架构(CSA)是两个Chiplet之间架构通信的重要因素。”Moshiko Emmer说道,“UCIe是允许进行这种通信的物理接口,你可以设计一个带有Chiplet 但不带有UCIe的2.5D和3D芯片。缺乏标准化的问题在于,你可以构建定制解决方案,就像大型和超大规模公司正在构建的那样,这给了他们很大的灵活性,因为只要物理连接并符合他们定义的某些架构规范,他们就可以做任何他们想做的事情。他们可以在两个不同的Chiplet之间通信。他们可以进行3D通信。他们可以进行2.5D通信。如果是多个Chiplet,他们可以进行不同类型的集成。”

标准化将有助于使这种方法更加普及。“标准化可以实现规模经济。”他说,“你可以吸引更多参与者参与其中。我们有很多公司参与硅片市场竞争,尤其是与20年前相比,你可以看到软件领域也发生了类似的情况。软件最初是由大公司驱动的,后来每个人都拥有一台电脑,就像大学里两个孩子坐在车库里发明了谷歌。你在硅片领域很少看到这种情况。这要困难得多,因为你需要更多的资金。另一方面,采用标准化的Chiplet技术,可以让规模较小的参与者以及目前不从事硅片业务的大型参与者加入游戏。”

Chiplet技术也为更多行业合作打开了大门。“理论上,这是一个好主意,因为如果我不需要尖端工艺技术来实现某些功能,那么我可以在较旧的工艺技术上构建Chiplet。”Rambus的杰出发明家Steven Woo说道,“内存标准就是一个例子。DDR4会在市场上销售10年,因此速度范围已经明确,一段时间后速度不会再变快。所以,我实际上并不需要尖端工艺技术来构建内存控制器、接口等等。也许我可以把它们放在Chiplet上,然后继续沿用较旧的工艺节点。既然标准规格没有变化,我又何必费心去做呢?”

一个持续的挑战是如何以一种几乎肯定行得通的标准化方式将所有东西连接在一起,但又不会产生过多的开销。Steven Woo表示:“目前业界并没有很多广泛遵循的标准。当然,还有BoW、UCIE以及许多其他提案。但当业界最终团结起来,确定一两个方案时,就能催生出一个更通用的Chiplet市场。如果你是像英特尔或AMD这样的垂直整合公司,你可以投入任何对你有意义的东西。但如果你在谈论Chiplet市场,就必须制定这些标准。”

选择使用哪种标准会对设备的架构和权衡产生影响。Eliyan战略营销副总裁Kevin Donnelly表示:“2D(有机基板)和2.5D(硅中介层/桥接器)水平Chiplet连接的设计使用类似的芯片间接口,例如BoW和UCIe,以及成熟的热/机械分析工具。然而,垂直3D连接的接口完全不同,其电气原理简单得多,但物理外形尺寸严格得多,并且热约束和机械约束极具挑战性。例如,由于上方DRAM堆栈的热约束,定制高带宽存储器(HBM)的早期设计人员无法在基础芯片中包含所需的逻辑,这让他们感到沮丧。”

这为芯片设计增添了新的亮点。“过去,考虑这些事情很重要,但不一定从一开始就在设计蓝图上进行。”Steven Woo说道,现在,这些事情从第一天起就纳入设计规划,它会影响到封装和可用的I/O数量等因素,因为I/O变得越来越重要。此外,我们看到,物理效应正一代又一代地成为架构的关键驱动因素。因此,物理限制——比如散热、供电、I/O数量——在很多方面都限制了布局以及散热等方式。这意味着你必须提前考虑这些事情,否则日后可能会陷入大麻烦。这并不是说过去业界没有合作,而是这促使业界更加紧密地合作,以确保架构师能够提前了解两年后市场上会出现哪些产品。从技术角度来看,如果先进封装不是未来最重要的发展方向,那么它绝对是推动和促成行业诸多积极变革的最重要因素之一。

这更加强调了早期的可行性和探索。“过去,PCB设计只是敷衍了事。”新思科技(Synopsys)产品管理总监Keith Lanier表示,“从事系统架构设计的人员用电子表格程序来做。他们可能有MATLAB模型或类似的东西,并且有自己的方法从架构层面判断系统是否能正常工作。那种日子已经一去不复返了。我们拥有更好的工具,能够尽早进行研究,并拥有具有物理感知能力的功能架构设计。关键在于,即使在编写任何一行RTL代码之前,你也必须开始考虑需要应用于系统的工作负载。你需要使用功能架构来驱动物理架构,然后将物理数据反馈回来,以便尽早调整功能架构。”

Chiplet的优势之一是它们可以用来调整设计以适应特定的用例和工作负载。但对于依赖标准化Chiplet的主流应用而言,这种灵活性和定制化程度将取决于Chiplet标准的制定严格程度。

“与汽车或工业应用相比,数据中心对Chiplet系统的要求有所不同。”弗劳恩霍夫IIS/EAS高效电子部门负责人Andy Heinig表示,“汽车和工业应用不需要达到最高的能效,而数据中心则需要非常高的能效。但像BoW和UCIe这样的协议效率不够高。因此,如果自行实施,效率会更高,因为你无需支持不必要的功能。从数据中心的角度来看,这是一个大问题。”

Chiplet旨在实现最高的性能或效率,而非与目标应用之外的设备实现互操作性。但市场上的其他公司通常希望Chiplet具有互操作性且经济高效,这使得他们在功耗和性能方面处于劣势。

Andy Heinig表示:“目前看来,尤其是在UCIe方面的开发最终会导致IP价格高昂。他们必须支持许多模式。对于某些更高的通信层,如果你认为可以在UCIe上使用PCIe,那么就需要PCIe IP,而这非常昂贵。这使得整个通信IP非常昂贵,这就是我们目前看到的。我们最初预计die-to-die接口的成本会很低,以便每个人都可以使用,但现在IP价格非常昂贵,这使得工业应用很难使用。汽车行业也是如此,因为汽车行业非常注重成本,会认真考虑IP是否从成本角度满足其需求。”

BoW的成本可能更低,但它缺乏UCIe那样的互操作性广度。“我们目前认为这是一个先有鸡还是先有蛋的问题。”Andy Heinig说,“我们需要更多原型演示,才能弄清楚哪些是真正必要的,因为有些开发还是PPT,有些人只是写下了对未来的期望,但并没有真正从清晰的应用角度出发。我们在其他协议上也看到过这种情况。它们是一步一步、一代一代地开发出来的,只加入了必要的内容。而我们的感觉是,标准中几乎包含了所有东西,之后再进行梳理非常困难。”

对于Chiplet来说,选择协议是一项重要的决定。“UCIe有针对电路板的协议,即使Chiplet彼此靠近(即使距离只有4~5毫米),如果想要高速通信,芯片之间的连接线仍然很大。”Ansys产品营销总监Marc Swinnen表示,“我们看到UCIe似乎是最常用的协议,但BoW和其他一些协议也在使用。EDA供应商开始推出专门针对这些设计的UCIe开发/实用程序套件。但专有协议(例如英伟达的NVLink)仍在使用,它们是整个Chiplet生态系统设计的重要组成部分。”

现在的一大挑战是一开始就权衡尽可能多的利弊,然后制定一个针对特定应用所需的优化计划。

Ansys产品管理总监Suhail Saif表示:“业内从事这些设计的客户和用户一直在进行权衡。这是每天都要做的事情。他们希望找到一个最佳平衡点,既不会在性能和容量上做出过多妥协,也不会在功耗上过度优化,同时又能控制功耗范围,以免给系统的其他部分带来负担。这是一个持续的挑战,即使是业内的功耗优化解决方案,也始终需要在优化不足和过度优化之间保持微妙的平衡。EDA解决方案能够为设计团队提供大幅提升功耗的建议,但它们缺乏巧妙地分析功耗对设计性能或功能影响的能力,因为它们实际上只关注功耗这一单一指标。这始终是一个挑战。”

Chiplet的灵活性

Chiplet的一大吸引力在于它能为设计团队提供极大的灵活性。无需重新设计整个多芯片设计,即可轻松更换Chiplet,这对于缩短产品上市时间并针对特定工作负载和应用而言是巨大的优势,但到目前为止,这种能力仅限于少数芯片制造商。

“微处理器公司确实利用了可重复使用部件所带来的灵活性。”Ansys的Marc Swinnen说道,系统有些部分他们无需在不同产品之间重新设计,因为它们的功能相同。他们只需将相同的芯片集成到一起即可。这适用于多CPU版本。你可以拥有8、12或24 CPU版本,只需添加更多Chiplet即可。可重用性是其中很重要的一部分,它在产品设计中提供的灵活性无疑正是他们充分利用的优势。因此,他们非常重视确保其尽可能地可重复使用。但始终存在一个权衡:是从一开始就完全定制还是重复使用?以苹果为例,他们拥有Arm的许可证,但他们不采用Arm预先设计的Arm公版架构版本。他们自己设计并进行最大程度的优化。但大多数人最好还是采用Arm优化过的软核。这始终是一个权衡。你随时可以将其推向极限并重新设计。“为了获得极致的优化速度,你可以自己动手,但这样做是否值得你投入时间和精力,从而获得更高的收益?或者,即使可重复使用的芯片需要一定的成本,你还是选择重复使用芯片更好?”

除了性能和功耗之外,其他关注点还包括可靠性和安全性。“说到可靠性,可以看看USB接口。”Marc Swinnen说道,“没有人会自己设计USB。USB的设计是经过安全测试的,而且你也知道你不想冒险通过所有可能的排列组合来验证自己的设计。采用现有的设计更安全,因为你知道它有效。Chiplet市场在概念上与IP市场并没有本质区别。细节更复杂,需要考虑的问题也更多,但我认为我们没有理由像克服IP那样克服这些问题。我们转向IP的原因仍然适用于Chiplet。”

然而,需要多少个Chiplet标准尚不清楚。“这肯定正在全面讨论和开发中,”Marc Swinnen说,“新标准必须比现在更丰富。有信号接口标准。还必须有一个热标准,而IP块以前从未有过这样的标准。还必须有一个机械轨道标准。还有厚度标准。你看,即使是今天的2.5D堆栈,有些芯片比其他芯片厚,他们必须在它们上面放置小型虚拟硅片,才能形成一个光滑的表面,方便散热器连接。因此,与常规IP相比,需要标准化的问题更多,但这只是相同原则的延续,只是涉及更多物理知识。”

后续Chiplet会怎样发展?

短期内,可以解决一些容易实现的难题,以推动Chiplet方法的发展,包括安全性、测试、功耗和时钟。长期问题在于弄清楚不同的Chiplet如何相互作用。

西门子EDA中央工程解决方案总监Pratyush Kamal表示:“对于其中一些,你必须让Chiplet更加自主。最终,Chiplet与传统芯片定义之间的界限将会模糊。我们往往会自欺欺人地认为Chiplet是一个需要先进封装的实体,需要与另一个Chiplet紧密集成。但Chiplet也可以独立于封装之外。在我看来,今天的芯片设计为独立工作。一旦所有底架标准化就位,未来的Chiplet就会慢慢呈现出这种样子。我刚刚改变了‘Chiplet’的定义,使其包含两点。第一,它需要与另一个Chiplet进行更高带宽的接口——高于通常的带宽。这种带宽应与其片上性能(片上总线)相当。第二,它要么依赖于另一个Chiplet的资源,要么负责管理它们以及底架资源。这才是最终使其成为Chiplet的原因,因为即使我们明天进行标准化,任务仍然会由少数Chiplet(而非全部)来委托和决定,而且它的架构会有层次结构。”

这意味着在创建微架构时,可能需要为一些目前尚不存在、可在以后添加的功能做好准备。Pratyush Kamal表示:“这可能是分配额外的寄存器空间,为以后可能出现的一些应用程序定位额外的一次性可编程内存空间。一旦进入软件层,一切都变得灵活,你可以做很多事情。但是,当芯片仍在制造或测试中时,没有软件加载。在设计Chiplet时要仔细思考。在没有软件的裸机模式下,你如何与另一个Chiplet通信?在没有任何编程的情况下,你将如何做到这一点?这非常关键。”

参考链接:https://semiengineering.com/chiplet-tradeoffs-and-limitations/

5.美国芯片关税征收倒计时,税率高达100%?半导体厂商屏息以待

美国总统特朗普最快本周宣布对进口芯片实施关税,市场预估税率可能介于25%~100%;法人指出,此芯片关税恐对台积电及中国台湾半导体厂商产生深远影响,新规则不排除以晶圆制造地(wafer out)来源征税,半导体厂商皆屏息以待。

厂商表示,中国台湾半导体产业被视为“硅盾”,但特朗普芯片关税政策可能削弱这一优势。若关税过高,美国客户可能转向其他国家/地区(例如韩国或日本)寻求替代供应商,或促使中国大陆加速自制芯片进程。同时,美国对台积电的依赖与地缘政治紧张局势,若加速运行“美国制造”目标,将使关税政策可能引发报复性措施,进一步扰乱全球供应链。

中国台湾IC设计厂商近日于法说会上强调,4月初运行的对等关税并未见重大订单调整,客户下单多采取稳定态度观望面对,惟对于半导体关税,厂商认为,采取晶圆产地征税,将使得美国客户面临进口关键零组件成本显著提高,首先冲击的就是于亚洲投片生产的美国芯片厂商。

若新制如市场推测,改以晶圆制造地认定征税,不排除推动部分产能回流美国本土,但预计供应链重组过程中,将出现采购周期拉长、运输递延等不确定性,必定影响企业获利,同时影响美国芯片厂商在全球的竞争优势。

厂商也强调,半导体属于上游产业,一旦芯片被征税,仍有高几率与能力可以向下转嫁,但由于科技产品不是只有单一芯片,多款应用芯片都进行成本转嫁后,终端产品售价就会出现惊人调整,因此,中国台湾半导体厂商近期关注焦点,也逐渐由特朗普政府变来变去的关税政策,转为关切终端消费需求受冲击程度为何。(工商时报)

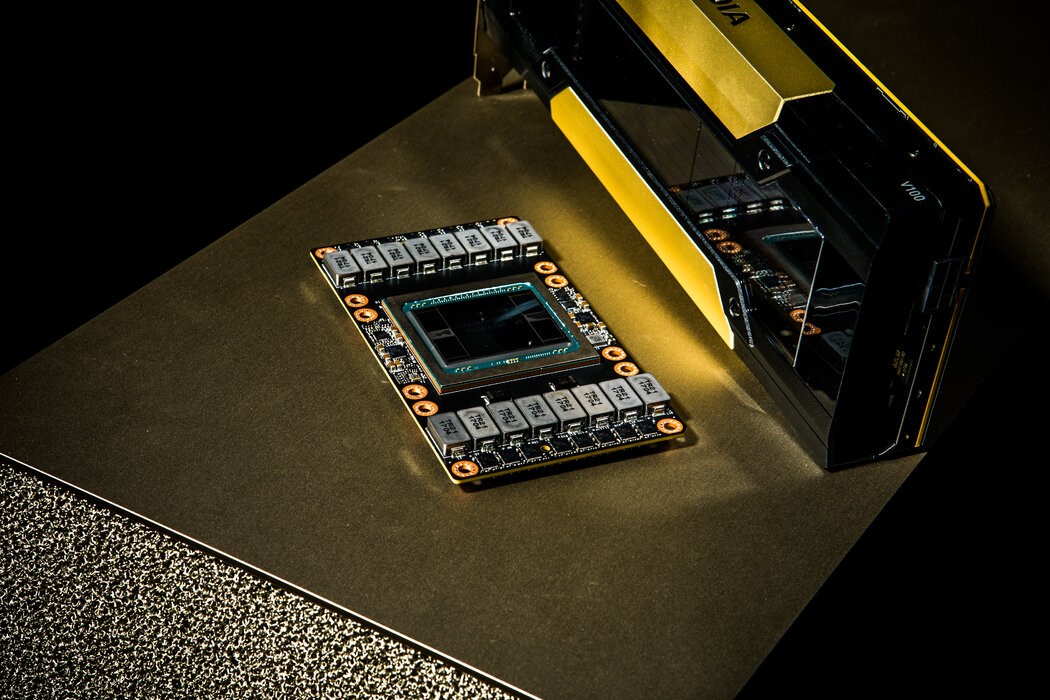

6.三星代工业务再遭打击,AMD放弃采用其4nm制程技术

三星代工厂近期发展不顺,其在3nm工艺制程上的困境已广为人知,导致该公司可能错失高通和英伟达等公司数十亿美元的订单。

此外,其传统制程的需求放缓,迫使三星关闭部分生产线以降低成本。AMD近期预计将采用三星的第四代4nm制程节点(SF4X),但据报道该公司已决定放弃。

AMD放弃该交易的原因尚不清楚。

三星代工厂于今年3月开始量产采用SF4X制程的芯片。三星自2021年以来一直在生产4nm芯片,并持续升级该制程技术。最新版本的4nm制程采用后端线路布线技术,可降低制造成本并提升芯片性能。

据报道,AMD原本计划采用三星SF4X工艺制造其服务器CPU I/O芯片,因为台积电的4nm产能不足,无法满足AMD的需求。三星或许是更具成本效益的选择,众所周知,三星与台积电展开激烈的价格竞争,以赢得客户。

目前尚不清楚具体发生了什么变化,但一份新报告称,AMD已决定不再采用三星的SF4X工艺来生产这些芯片。或许是为了获得台积电的产能配额,又或许是为了与三星达成更有利的协议,但无论如何,这只会加剧三星代工厂的挑战。

7.美议员拟推新法案:追踪英伟达AI芯片去向,遏制对华偷运

一位美国议员计划在未来几周内提出一项法案,以核实英伟达等公司生产的人工智能(AI)芯片售出后的去向。

这项密切监控芯片的举措得到了美国两党议员的支持,旨在解决有关英伟达芯片广泛偷运的报道,这些行为违反了美国的出口管制法规。

英伟达芯片是创建AI系统(例如聊天机器人、图像生成器等)的关键组件。美国总统唐纳德·特朗普和他的前任乔·拜登政府都逐步加强了对英伟达芯片对华出口管制。

不过,有报道称,部分芯片仍在继续流通,英伟达也公开声称无法追踪售出的产品。

美国伊利诺伊州民主党众议员Bill Foster曾担任粒子物理学家。他表示,追踪芯片售出后的技术已经唾手可得,其中大部分技术已经内置于英伟达的芯片中。

Bill Foster在其科学生涯中成功设计了多款计算机芯片,他计划在未来几周内提出一项法案,指示美国监管机构在两个关键领域制定规则:追踪芯片,确保它们在获得出口管制许可的授权范围内;以及阻止未获得出口管制适当许可的芯片启动。

Bill Foster表示,目前已有可靠报告显示芯片偷运活动正在大规模发生,其中一些报告尚未公开披露。

据分析公司SemiAnalysis称,DeepSeek AI系统的出现对美国系统构成强劲挑战,采用的英伟达芯片被禁止出售给中国。新加坡检察官已指控三名人员犯有欺诈罪,案件涉及可能包含英伟达芯片的服务器。

虽然尚未广泛应用,但验证芯片位置的技术已经存在。据消息人士透露,出于安全目的,Alphabet旗下谷歌已经在其庞大的数据中心网络中追踪其内部AI芯片和其他芯片的位置。

Bill Foster的法案提议将给予美国商务部六个月的时间来制定强制使用该技术的法规。

Bill Foster的法案得到了众议院“特别委员会”资深成员Raja Krishnamoorthi等民主党的支持。Raja Krishnamoorthi在一份声明中表示:“芯片位置验证是我们应该探索的一种创新解决方案,以阻止这种偷运活动。”

共和党人也对此表示支持。特别委员会主席、众议员John Moolenaar表示:“特别委员会得到两党的大力支持,要求英伟达等公司在其高性能AI芯片中内置位置追踪功能——而且这项技术已经存在。”

验证芯片位置的技术将依赖于芯片与安全的计算机服务器通信,该服务器将利用信号到达服务器所需的时间来验证芯片的位置,而这一概念依赖于计算机信号以光速传播的认知。

华盛顿智库Institute for Progress前工程师兼新兴技术政策主管Tim Fist表示,这种追踪技术将提供芯片的总体、国家/地区级位置信息。但这比美国商务部负责执行出口管制的机构工业和安全局(BIS)目前掌握的信息要多得多。

Tim Fist说:“BIS不知道哪些芯片一旦流向海外,就应该作为潜在的重点调查对象。通过位置验证,他们现在至少把世界上现有的芯片分为两类:一类很可能没有被偷运,另一类则需要进一步调查。”

Bill Foster的第二个立法目标是阻止未获得美国出口管制适当许可的AI芯片启动,这在技术上比位置验证更复杂,但他表示,现在是时候开始讨论这两项措施了。

“我们已经获得了足够的意见,我认为现在我们可以与实际的芯片和模块供应商进行更详细的讨论,并讨论‘将如何实际实现这一点?’”Bill Foster表示。

评论

文明上网理性发言,请遵守新闻评论服务协议

登录参与评论

0/1000